时间:2026-04-12 来源:FPGA_UCY 关于我们 0

在Xilinx FPGA上快速实现JESD204B接口,可通过以下步骤完成,并结合设计示例与调试建议优化实现效果:

一、JESD204B协议层级与Xilinx实现架构

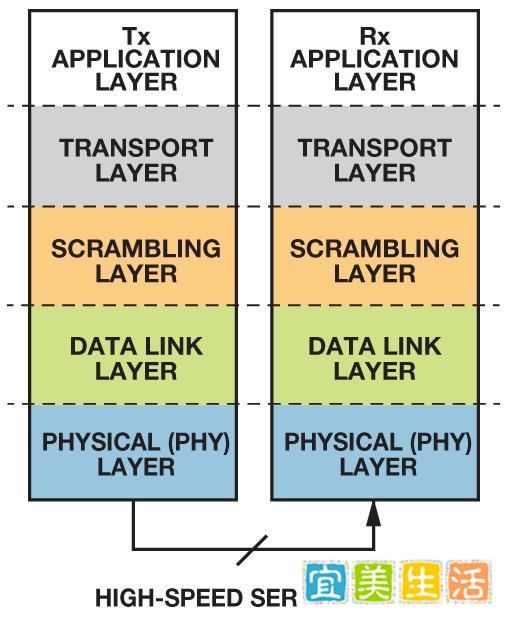

JESD204B协议分为四层:

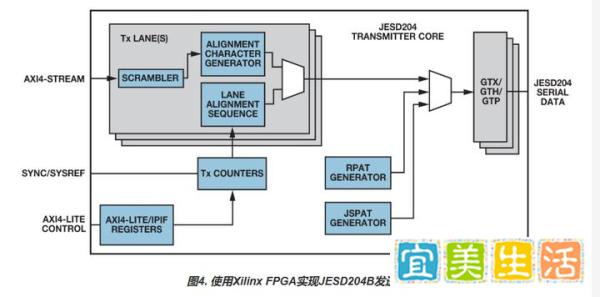

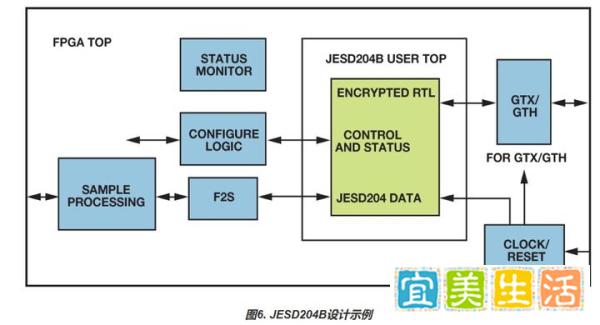

Xilinx实现方式:提供加密的JESD204 IP核(通过Vivado设计套件交付),包含发送/接收模块(对应图4、图5中的链路层与部分物理层功能),用户需自行实现传输层(F2S模块)及调试辅助模块。物理层的8B10B编码器/解码器集成在GTX/GTH收发器中。

图1:JESD204B协议四层架构二、Xilinx FPGA设计示例与关键步骤1. 设计简化流程

图4/5:Xilinx FPGA上的发送器(左)与接收器(右)结构2. 符号对齐优化三、调试与监测关键点1. 链路状态监测2. 信号质量评估

图6:基于Xilinx IP核的简化设计框架四、设计注意事项时钟树设计:全局时钟需覆盖内部PLL、并行接口、JESD204核及用户逻辑,避免时钟偏移导致数据采样错误。资源分配:加密RTL模块直接连接GTX/GTH,减少中间逻辑层级以降低延迟。调试接口:预留ILA(集成逻辑分析仪)触发信号,实时捕获SYNC、解码错误等关键状态。五、结论

在Xilinx FPGA上实现JESD204B接口需重点关注以下环节:

通过上述方法,可快速完成JESD204B接口设计,并满足高速数据转换器(如ADC/DAC)与FPGA的确定性延迟传输需求。

上一篇:FPGA芯片基础知识