时间:2026-04-12 来源:FPGA_UCY 关于我们 0

注:本文内容来源于B站UP主小梅哥爱漂流的视屏内容,本人整理出来前三节课的视频笔记,对视频内容感兴趣的同学可以去看看小梅哥的视频,视频链接为https://www.bilibili.com/video/BV1NE411h7qP?p=4&t=2584。FPGA内部基本结构

现场可编程门阵列FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

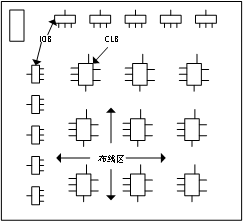

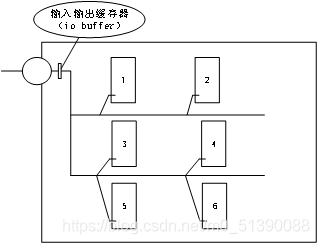

FPGA的基本结构示意图如图所示,它由三个可编程单元和一个用于存放数据的静态存储器组成。这三种可编程的单元:输入输出(I/O)模块、可编程逻辑模块和互连资源IR,如下图所示。

实现基本逻辑关系的电路被称为门单元。

可编程输入输出块包括有:输出寄存器、输入寄存器、输出使能寄存器、输入延迟链、输出延迟链、上拉电阻;

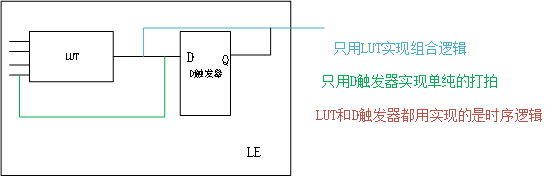

可编程逻辑块的示意图如下图所示,LUT是指查找表。

查找表概述

Xilinx生产的FPGA采用SRAM——查找表类型的可编程原理。

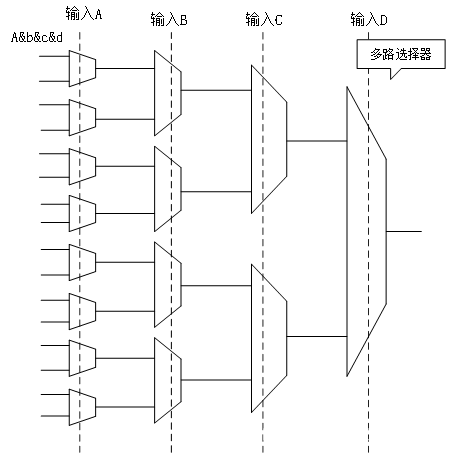

一个N输入的查找表可以实现N个输入变量的任何逻辑功能。

当输入为0,选择上方通道,为1选择下方通道,四输入查找表内部结构如下图所示。

通过查找表,我们可以实现各种各样的逻辑电路。

数据传输路径

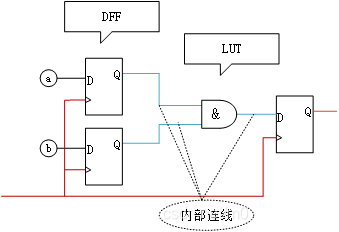

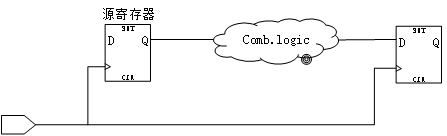

所以在数据传输路径的延迟时间主要包括内部走线延迟 、组合逻辑单元延迟n 和内部走线延迟n。数据传输的基本框图如下图所示

如果我们不考虑时钟的延时,我们可以根据数据传输路径分析一下整个数据传输的延时。

Tco:时钟上升沿到达D触发器 到数据传输出到Q端的延迟时间

Tsu:建立时间,目的寄存器自身特性决定,在时钟新年好上升沿到达其时钟接口时,其数据输入端(D)必须提前Nns稳定下来,负责无法保证数据正确存储。

时序分析模型

时钟树资源,全局时钟树能够让时钟信号达到寄存器的差距比较小,但是不能保证完全一致。时钟树结构示意图如下图所示:

时序分析的目的:通过分析FPGA设计中各个寄存器之间的数据与时钟传输路径,来分析数据延迟和时钟延迟之间的关系。系统中所有寄存器都能存储正确的寄存数据。

数据与时钟传输路径,由EDA软件,通过针对于某个特定的器件布局布线得到的。

时序约束的两作用:

①告知EDA软件,该设计需要达到怎样的时序指标,然后EDA软件就会根据时序约束的哥哥参数,尽快优化布局不信啊,以达到该约束的指标。

②协助EDA软件进行分析设计的时序路径,以产生相应的时序报告。

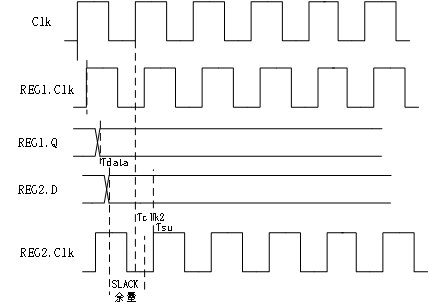

1、时序分析的基本模型,如下图所示。

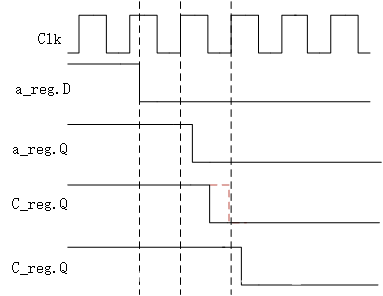

基于时序分析模型,考虑时钟的延迟,我们得出下图波形图

分析数据传输路径建立时间余量的基本公式:Tclk1+Tdata+Tco=0

Tskew=(Tclk2-Tclk1)

令Slack=Tclk+Tskew-Tsu-Tdata-Tco

Slack就是建立时间余量且要求Slack>=0;

基于建立时间余量的概念,我们有最高时钟频率的概念,也就是余量为0时的时候的最大时钟频率。

Tclk:时钟周期

Tclk1:时钟信号从时钟源端口出发到达源寄存器时钟端口的时间

Tclk2:时钟信号从源寄存器时钟端口出发到达目的寄存器时钟端口的时间 Tco:时钟上升延到寄存器时钟端到数据输出到寄存器Q端口的时间

Tdata:时钟从源寄存器Q端出发到目的寄存器D端口的时间 Tsu:寄存器要求其数据端口的值必须提前于时钟上升沿达到其时钟端口的时间值。

Tskew:始终从源端口出发达到目的寄存器和源寄存器时钟端口时间的差值。

Slack:数据需求时间和数据到达时间的差值,如果为正值,则表明数据被目的寄存器正确接收;如果为负值则反之。

Tclk1+Tdata+Tco:数据到达时间 Tclk+Tclk2-Tsu:数据需求时间

知识补充

问题:这个代码所描述的逻辑电路在cyclone IV E的EP4CE10F17C8(65nm)这个器件能最高运行在多少频率的时钟?

这个需要时序分析软件告诉我们答案。

时序分析一定要基于特定器件(该器件需要具体到一个特定型号的特定速度等级);

时序分析一定是基于某个逻辑设计在该特定期间上经过布局布线之后的网表(该网表包含了设计中每个逻辑具体在该器件的什么资源上面实现,而且还包括该资源在器件内的具体位置,还包括信号从每一个节点传输到下一个节点的具体延迟时间)。时序分析不是在对代码分析,而是在对真实的门级传输路径进行分析。

如果用户没有对时钟信号加约束,软件就会自动对分析出的时钟信号加入约束,这个约束会按照最大的可能来约束.。

温度越高,芯片内部信号传输速度越慢,因为温度可以改变硅片材料,泄漏电流和电子移动能力等特性,导致较高温度下芯片内信号传输速度变慢。传输速度变慢,延时就会增加,余量就会减少,从而导致时序不满足。

下一篇:FPGA芯片基础知识