时间:2026-02-03 来源:FPGA_UCY 关于我们 0

欢迎各位未来的硬件设计师!如果您是一名工程专业的学生,即将踏入现场可编程门阵列 (FPGA) 的世界,那么您来对地方了。本文将指导您完成第一次实验课程,我们将使用功能强大的 Xilinx Vivado 设计套件来实现一个简单的数字电路。

我们将从零开始:创建一个项目,编写第一行Verilog代码,模拟设计,最后对FPGA板进行编程,以在现实世界中看到我们的作品。那么,让我们马上开始吧!

什么是FPGA?

在深入了解工具之前,让我们先快速了解一下我们要使用的技术。现场可编程门阵列 (FPGA) 是一种非常神奇的硅芯片。与功能固定的普通微处理器(例如笔记本电脑中的微处理器)不同,FPGA 就像一张白纸。您可以对其内部电路进行编程,使其充当您能想象到的任何数字系统——从简单的逻辑门到复杂的处理器,或者介于两者之间的任何系统。

你可以把它想象成一套数字乐高积木,你可以在芯片制造完成后定义每个模块之间的连接方式。我们使用一种叫做Verilog HDL(硬件描述语言)的语言来“告诉”FPGA我们希望它变成什么样子。不同的计算机行业对FPGA板卡有不同的定义,我们将使用NEXYS A7。

NEXYS A7 FPGA 训练板

FPGA设计的五步历程

在 Vivado 中,将 Verilog 代码转换为 FPGA 上的可运行电路涉及五个关键步骤:

综合: Vivado 将您编写的人类可读的 Verilog 代码转换为基本逻辑门的网表。映射:然后将此门级网表映射到目标 FPGA 上可用的特定组件(如查找表或 LUT)。布局:该工具确定 FPGA 上这些映射组件的最佳物理位置,以最大限度地减少延迟并有效利用空间。布线:FPGA 内部的可编程连接(导线)配置为将所有放置的组件连接在一起。比特流生成:最后,布局布线后的设计被转换为 .bit 文件,这是一个包含 FPGA 所有配置信息的二进制流。

将此比特流加载到电路板上,即可对 FPGA 进行编程,使其按照您的设计运行。

动手实践:构建一个简单的与门

本教程的目标很简单:在 Nexys A7 FPGA 板上实现一个2输入与门。与门只有在两个输入都为“ 1 ”时才输出“ 1 ”。

步骤 1:在 Vivado 中创建新项目启动Vivado IDE。你会看到一个启动屏幕。

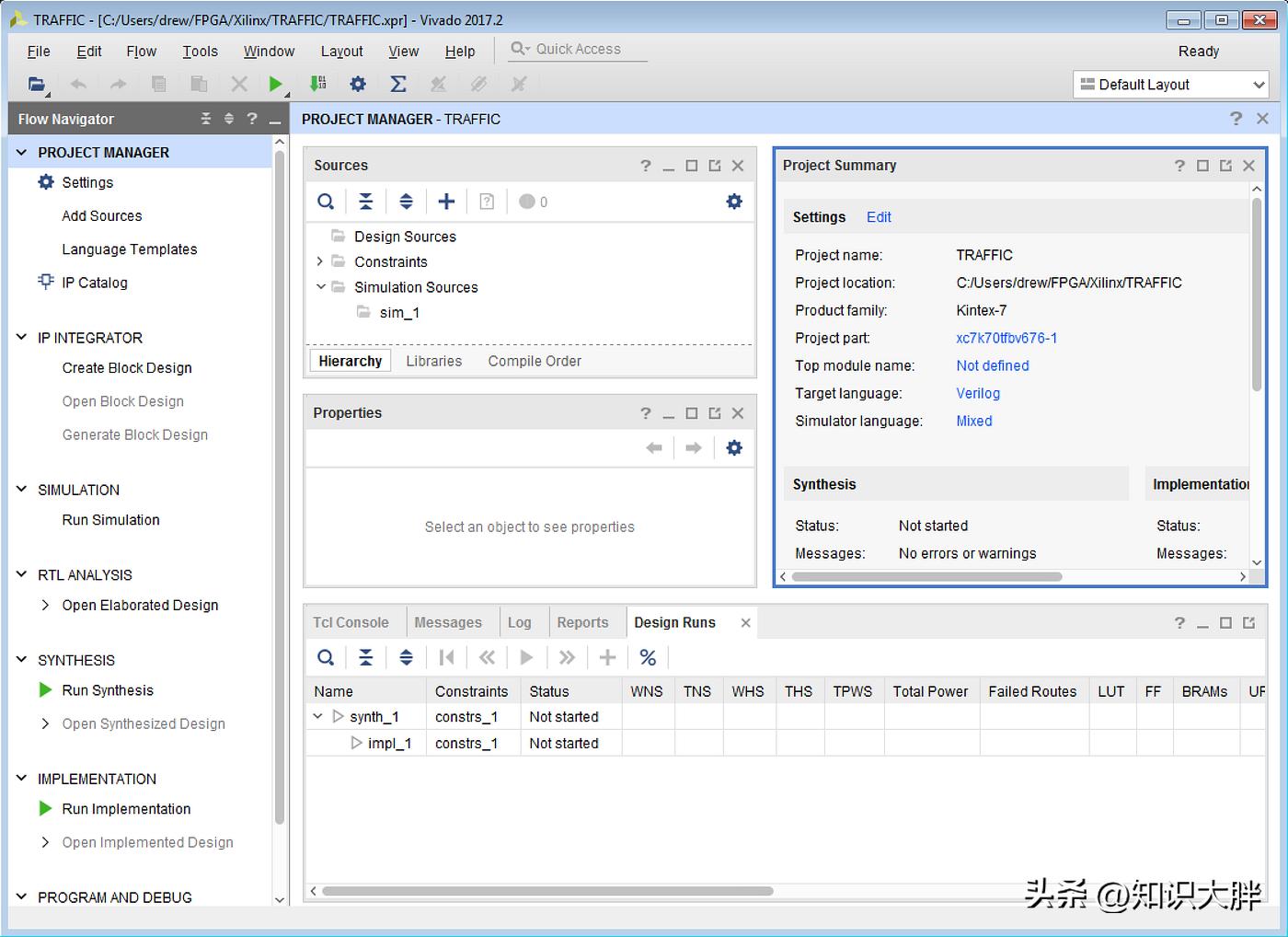

Xilinx 项目导航器窗口

点击“快速入门”下的“创建项目”。向导将引导您完成操作。为您的项目选择一个名称和一个地点。选择“RTL 项目”作为项目类型。RTL 代表寄存器传输级,是一种常用的数字电路设计方法。在“添加源文件”窗口中,我们可以选择在此处创建HDL文件,也可以在设置项目之后再创建。我们现在先跳过这一步。添加约束文件也是如此,我们稍后再讨论。在“默认部件”窗口中,您需要选择以下选项才能在 NEXYS A7 板上实现设计:

7. 查看摘要并点击“完成”。您的项目现已创建完成!

步骤 2:编写 Verilog 代码

项目设置完成后,主编辑器窗口将会出现。

主窗口

现在,让我们用 Verilog 描述一下我们的与门。

在“源”窗口中,单击“+”图标,然后选择“添加或创建设计源”。点击“创建文件”,根据您的喜好命名(例如:MyANDgate ),并将文件类型设置为Verilog。此时会弹出一个新窗口,供您定义模块的端口(输入和输出)。您可以跳过此步骤,因为您需要在代码中定义这些端口;或者,您可以按如下方式填写:

4. 单击“确定”和“完成”。Vivado 将为您生成一个模板。

5. 在“源文件”面板中,双击MyANDgate.v将其打开。典型的与门 Verilog 代码如下所示:

module myANDgate(

input a ,

input b ,

output c

);

and o1(c, a , b ); // 这是Verilog 中用于 AND 门的内置原语

endmodule步骤 3:模拟设计

在对电路板进行编程之前,最好先检查一下逻辑是否正确。我们使用测试平台来完成这项工作。

再次点击“添加源”,但这次选择“添加或创建模拟源”。创建一个名为“ test ”的新文件。打开此文件并粘贴以下测试平台代码。此代码将所有可能的输入组合(00、01、10、11)应用于我们的与门。

module test1;

// Inputs

reg a;

reg b;

// Outputs

wire c;

// Instantiate the Unit Under Test (UUT)

MyANDgate uut (

.a(a),

.b(b),

.c(c)

);

initial begin

// Initialize Inputs

a = 0; b = 0; #100; // Wait for 100 time units

a = 1; b = 0; #100;

a = 1; b = 1; #100;

a = 0; b = 1; #100;

a = 1; b = 1; #100;

end

endmodule4. 保存文件。现在,在左侧的流程导航器中,转到“仿真”>“运行仿真”>“运行行为仿真”。

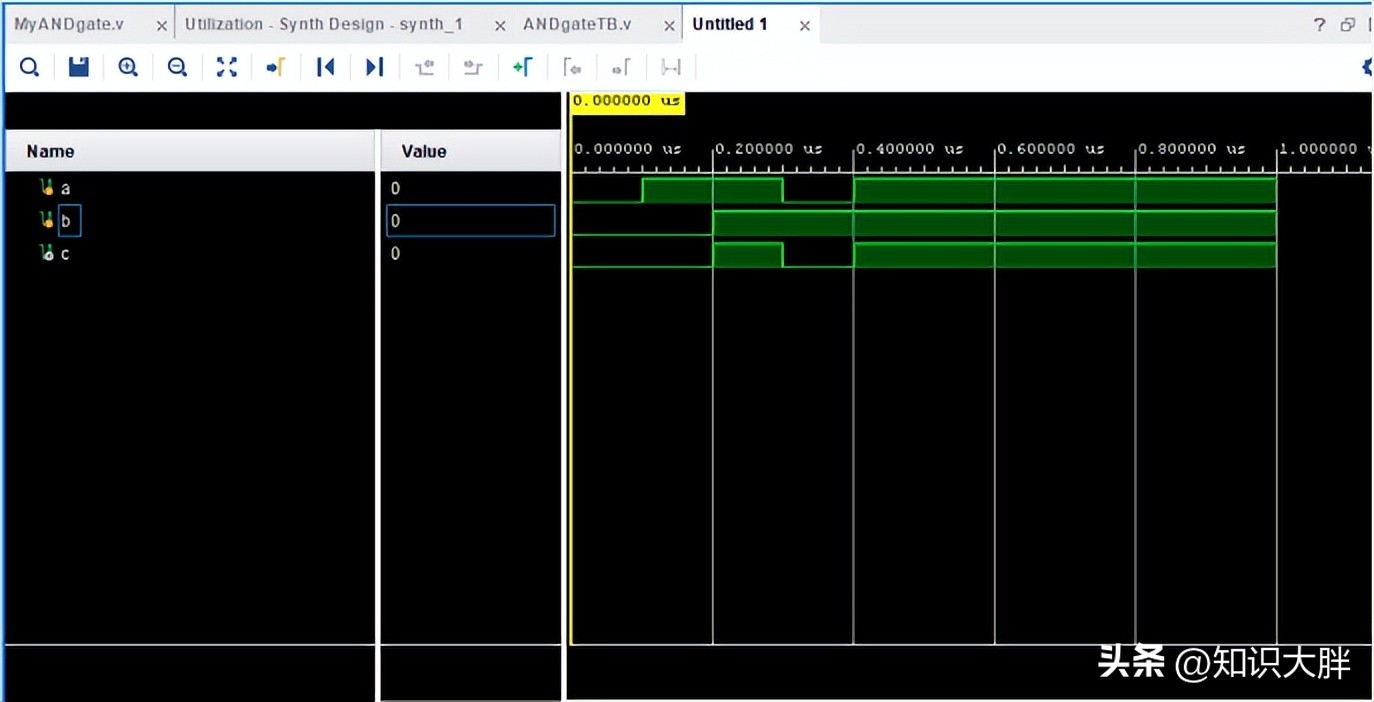

5. 此时会打开一个波形窗口,显示输出如何随输入变化而变化。验证输出c仅在 a和b都为“1”时才为“1”。

模拟设计

在FPGA上实现设计

这是最激动人心的部分!现在我们将把虚拟设计连接到FPGA的物理引脚上。

步骤 4:添加约束文件

Nexys A7 开发板带有物理开关和 LED。我们需要告诉 Vivado 输入a连接到特定的开关,输出c连接到特定的 LED。我们通过约束文件(.xdc)来实现这一点。

点击“添加源”,选择“添加或创建约束”,然后为您的文件命名。打开此文件并添加以下几行:

## 开关

set_property - dict { PACKAGE_PIN J15 IOSTANDARD LVCMOS33 } [get_ports a];

set_property - dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports b];

## LED

set_property - dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports c];此代码将端口a映射到开关0 (引脚 J15),端口b映射到开关1 (引脚 L16),端口c映射到LED 0(引脚 H17)。

步骤 5:生成比特流并对电路板进行编程

我们快到了!

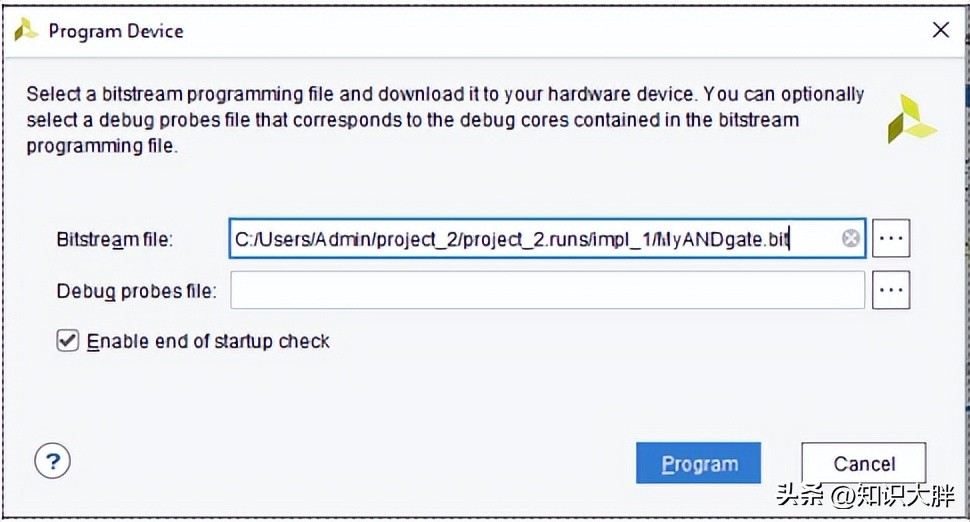

在流程导航器中,单击“生成比特流”。Vivado 将运行综合、实现,最后生成 .bit文件。这可能需要一分钟时间。现在,通过 USB 将 Nexys A7 开发板连接到电脑并开机。在 Vivado 中,打开“硬件管理器”,然后单击“打开目标”>“自动连接”。检测到开发板后,点击“编程设备” 。此时会弹出一个对话框,显示.bit文件的路径。点击“程序”。

位文件路径

如果一切顺利,您将在控制台中看到成功消息。

步骤 6:在真实硬件上进行测试

关键时刻到了!在您的 Nexys A7 主板上:

只有当两个开关都处于开启(向上)位置时, LED 才会亮起。恭喜!您已成功在 FPGA 上设计、仿真和实现了一个数字系统。