时间:2026-02-02 来源:FPGA_UCY 关于我们 0

文章概述

本文深入探讨了资源受限型应用中FPGA的有效利用策略,以满足行业对高度灵活且特定应用的逻辑需求。文章首先回顾了选择FPGA时需考虑的关键设计标准,随后以Altera公司经过功率和成本优化的的FPGA产品组合为例,详细阐释了不同产品线如何精准匹配特定应用场景。最后,文章着重强调了开发套件与评估板在加速FPGA设计原型开发及验证过程中的至关重要性。

资源受限的嵌入式系统对可配置逻辑的需求与日俱增。边缘 AI、机器视觉和工业自动化等应用需要灵活的应用特定逻辑,以满足不断变化的性能需求,同时在严格的功耗、尺寸和成本限制内运行。现代现场可编程门阵列 (FPGA) 可以满足这些相互竞争的需求。

选择 FPGA 时应注意的事项

为资源受限型系统选择FPGA需要考虑多种设计要求,并按照这些要求匹配正确的解决方案。有多个关键的 FPGA特性需要考虑:

Quartus Prime 提供了对开发人员友好的体验、广泛的预建逻辑块目录以及自动将这些逻辑块互连的能力,从而使 FPGA 设计更加易于实现。该工具集成了常用的 AI 和机器学习 (ML) 工作流,能够让使开发人员在 FPGA 上部署 Linux 和 Zephyr 等流行的操作系统 (OS)。

上述功能可大大加快 FPGA 的设计速度,因此在选择器件时,工具功能也是一个重要的考虑因素。

面向高级嵌入式工作负载的高性能计算

为了说明设计要求如何影响 FPGA 的选择,不妨从需要超高计算密度、带宽和集成度的高端应用入手。下面我们以高级边缘 AI 应用和高性能工业网关为例作详细分析。

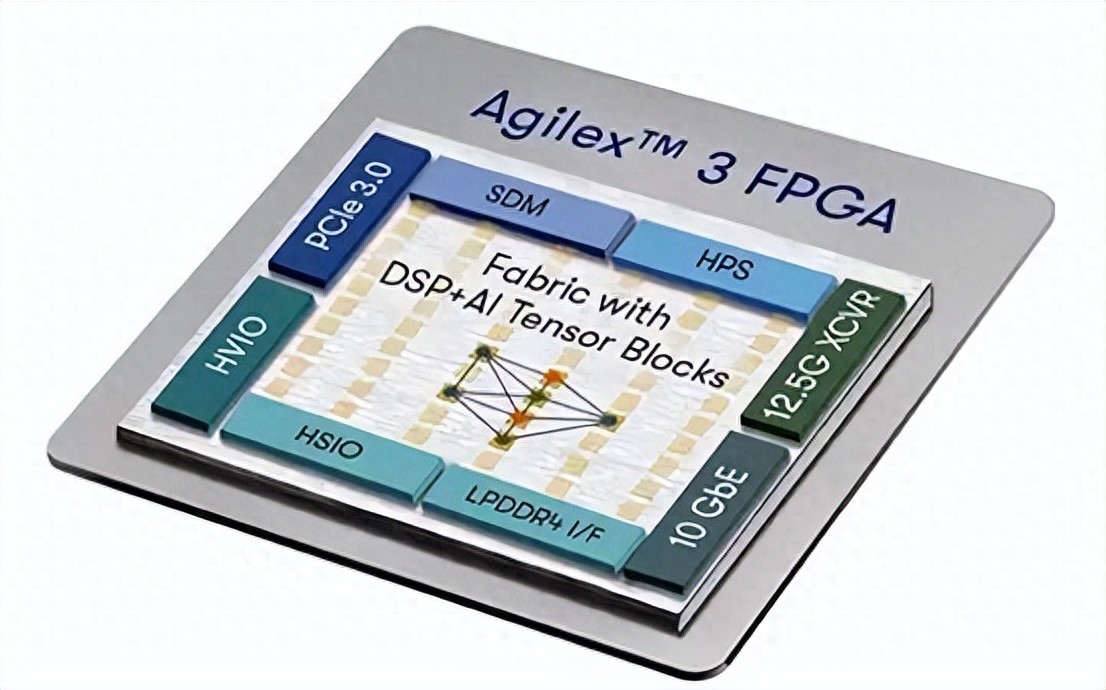

Agilex 3FPGA(图 1)专为满足这些应用需求而设计,可提供最高 135K LE。这些芯片有纯FPGA和片上系统 (SOC) 两种类型。SOC器件集成了双核 800 兆赫 (MHz)Arm®Cortex®-A55,能够让 FPGA处理复杂的软件堆栈,如人机界面 (HMI) 或网络堆栈。

这种可编程结构具有 AI 张量块,能够提供高达每秒 2.8 万亿次 INT8 运算(TOPS)。这些张量块支持各种计算格式,包括 FP16、FP19、FP32 和 BFLOAT16,并进行了优化,实现了对 AI 工作负载的高效执行。此外,还包括可变精度 DSP 块,为通用信号处理提供高达每秒 180 千兆次浮点运算 (GFLOPS) 的性能。

图 1:Agilex 3 以其高性能 DSP 和 AI 张量模块而著称。(图片来源:Altera)

高速连接是 Agilex 3 架构的另一个优势。收发器支持高达每秒 12.5 千兆比特 (Gb/s) 的数据传输速率,并提供用于 PCIe 3.0、万兆位以太网 (GbE) 和 LPDDR4 存储器接口的强化 I/O 块。对 IEEE 1588 精确时间同步的支持进一步增强了其对实时工业网络的适用性。

A3CZ135BB18AE7S器件展示了该系列的功能。它包括 135K LE、184 个 DSP 块,并提供 2.54 TOPS。

复杂系统的高级集成

对于工业自动化和中程视觉系统等应用而言,原始计算能力的重要性可能不如对带有大量定制逻辑和 I/O 的复杂配置的支持能力。Cyclone V FPGA非常适合这些应用场景,提供最高 300K LE 和广泛的高速接口。与 Agilex 3 一样,这些芯片也有纯FPGA和 SOC两种变型。其中 SOC器件集成了双核 Arm Cortex-A9。

这些芯片中的可编程结构包括可变精度 DSP 块,支持三重 9 × 9 和双重 18 × 18 定点乘法,以及 27 × 27 定点或浮点乘法。这些块可用于高级信号处理和 AI。

广泛的 I/O 组合支持多种电压等级和接口类型。强化逻辑块可实现先进的高速连接,包括 PCIe 2.0、DDR3 控制器和收发器,运行速度高达 6.144 Gb/s。

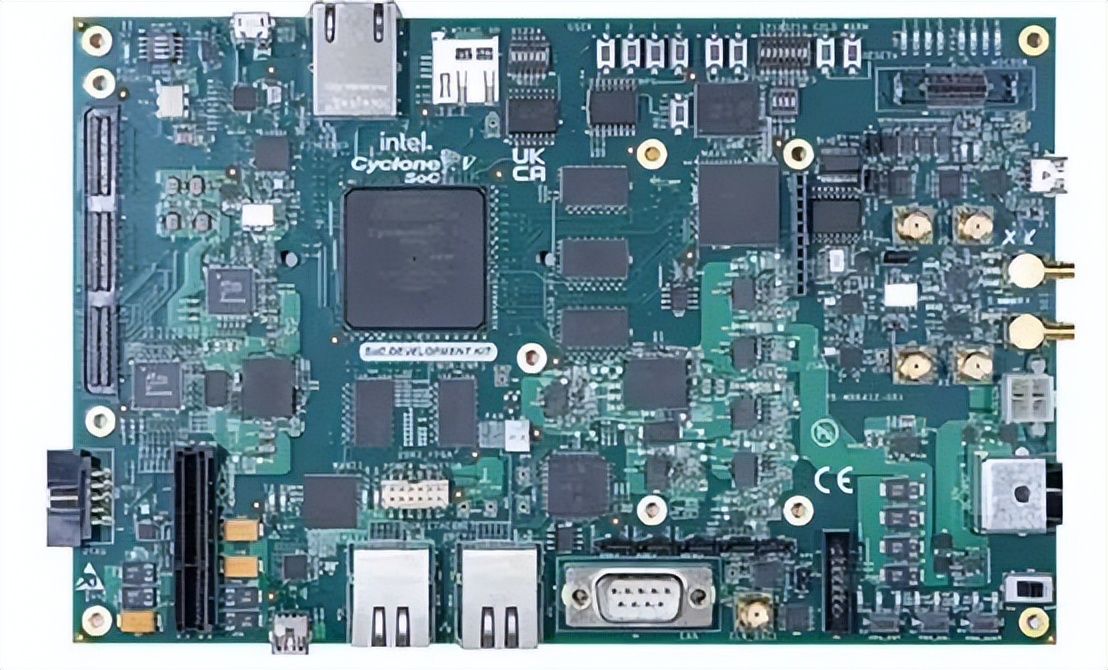

开发人员可以使用DK-DEV-5CSXC6N-B 开发套件评估 Cyclone V SOC系列(图 2)。该套件专为快速开发复杂的高吞吐量系统原型而设计。

图 2:DK-DEV-5CSXC6N-B Cyclone V 开发套件支持高性能原型开发。(图片来源:Altera)

该套件有几个显著特性:

该电路板采用5CSXFC5D6F31C8N 器件,包括一个运行频率为 600 MHz 的双核 Arm Cortex-A9 处理器、85K LE、87 个 DSP 块和 288 个 I/O 引脚,封装为 31 mm × 31 mm 的 896-FBGA。

采用紧凑型封装的高能效可配置逻辑器件

许多应用都受到空间和功耗的严格限制。例如传感器接口、电源定序和外设控制。MAX 10系列等FPGA为这些情况提供了有效的解决方案。MAX 10 器件的配置从 2K LE 到 50K LE 不等,封装尺寸小至 3 mm × 3 mm。

省电功能是 MAX 10 系列最显著的属性之一。内置睡眠模式可将动态功耗降低 95% 。借助片上闪存,器件还可在 10 毫秒 (ms) 内完全断电并恢复运行。

单电源选项进一步简化了供电。这使得 MAX 10 器件特别适合用于功率域可能需要先于系统其他部分联机的监控场合。

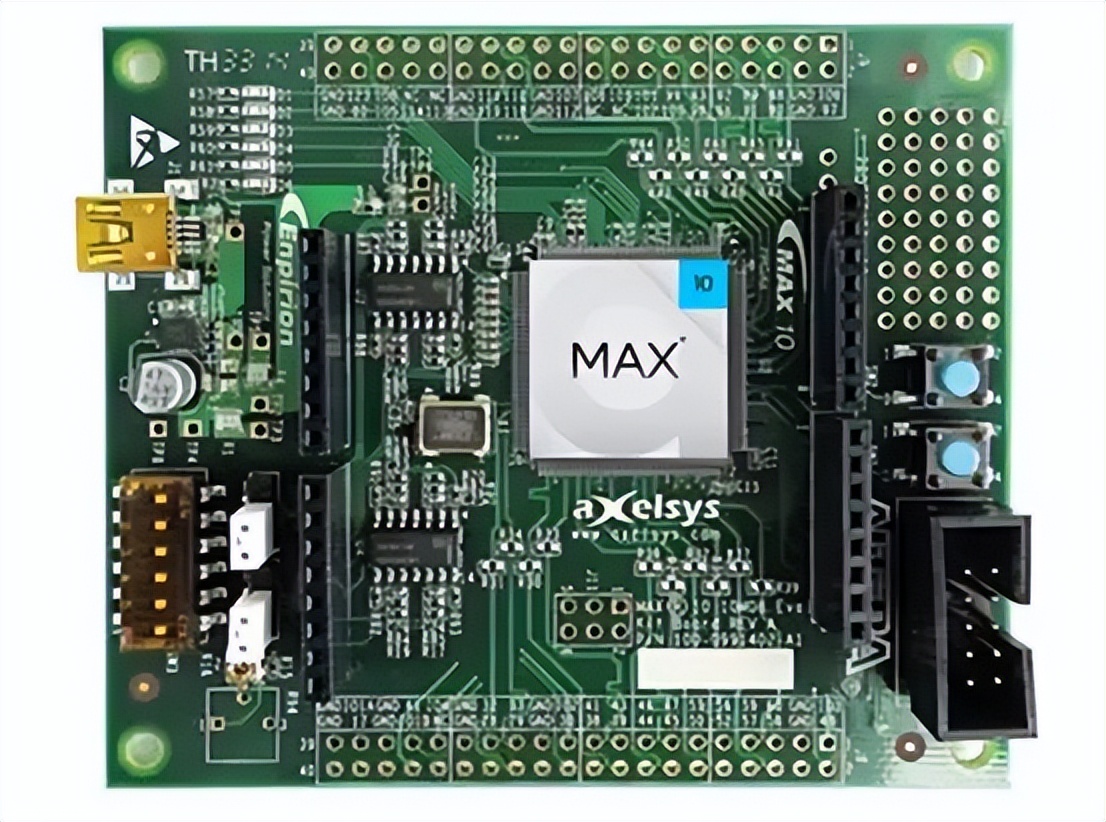

对 MAX 10 感兴趣的开发人员可以使用EK-10M08E144 MAX 10 FPGA评估板(图 3)对该系列进行评估。该电路板可通过Arduino UNO R3 连接器和测试点访问外部信号,其布局设计可支持对 ADC性能和整体电源行为的测量。

图 3:EK-10M08E144 MAX 10 FPGA 评估板可轻松访问关键 I/O。(图片来源:Altera)

电路板采用10M08SAE144C8G器件,包括 8K LE 和一个 ADC,封装为 144 引脚 LQFP。除内置硬件资源外,该 FPGA还支持基于 RISC-V 的 NIOs V 软处理器,无需外部微控制器单元 (MCU),设计人员即可实现轻量级控制功能。

适合中程应用的均衡性能

有些应用需要更大的逻辑和 I/O 容量,而入门级 FPGA无法提供。例如传感器融合、运动控制和芯片到芯片桥接。Cyclone 10 LP FPGA为满足这些要求,在器件中提供了多达 120K 的 LE 和 525 个 I/O 引脚,并针对成本敏感型应用中的功率和带宽平衡进行了优化。

与 MAX 10 一样,该系列包括适用于滤波、控制回路和基本 AI 推断等工作负载的 DSP 块。与MAX 10 不同,Cyclone 10 LP 器件集成了真正的 LVDS 收发器和片上终端 (OCT),以支持高速数字接口。

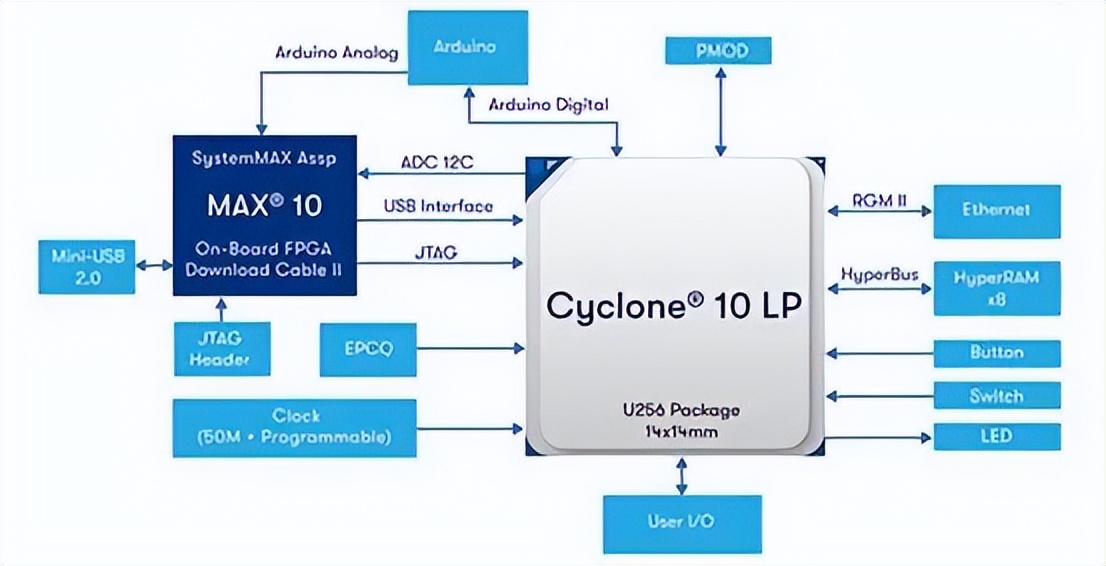

对 Cyclone 10 LP 感兴趣的开发人员可以使用EK-10CL025U256 Cyclone 10 评估套件(图 4)对该系列进行评估。该电路板提供 Arduino UNO R3 和Digilent Pmod 连接器,扩展方便简单。其他特性包括 GbE、USB2.0、128 Mb SDRAM 和 64 Mb 闪存。

图 4:EK-10CL025U256 Cyclone 10 评估套件支持轻松外设扩展。(图片来源:Altera)

该电路板采用10CL025YU256C8G器件,包括 25K LE、66 个 DSP 块和 150 个 I/O 引脚,封装尺寸为14 mm × 14 mm。与 MAX 10 一样,Cyclone 10 LP 系列也支持 NIOs V 软处理器。

结语

现在,设计人员在嵌入式系统中实现定制逻辑时要比以往任何时候都更加灵活。高性能应用可从集成了 AI 加速器的 FPGA 中获益。低功耗设计可以利用具有睡眠模式的器件。I/O 密集型系统可以利用具有大量引脚数和高速接口的芯片。重要的是,所有这些功能都可以通过易于使用的工具包,在资源受限型嵌入式系统的严格限制下实现。

小编的话

在资源受限型应用中,FPGA凭借其低功耗、小尺寸及可重配置特性展现出独特价值,而精准选型作为实现FPGA高效能的前提,对平衡功耗、性能、成本及开发效率至关重要,直接关乎产品的市场竞争力和实际表现。相信本文能过够为您的设计提供有益的参考和帮助。您在采用FPGA进行相关设计及选型有哪些经验,或有哪些疑问?欢迎留言,和DigiKey的朋友们一起分享交流!