时间:2026-04-16 来源:FPGA_UCY 关于我们 0

FPGA(现场可编程门阵列)的在线调试是硬件开发过程中不可或缺的一环,它允许开发者在硬件实际运行时监测和调试电路逻辑。以下是基于Altera的Quartus II和Xilinx的Vivado工具的FPGA在线调试方法简单总结。

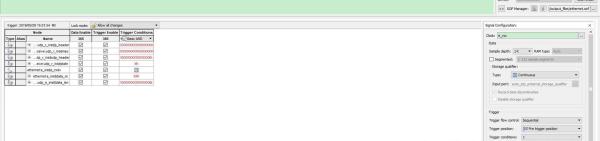

Altera Quartus II 在线调试方法

打开SignalTap工具:

在Quartus II中找到SignalTap工具,并启动。

设置参数:

设置SOF文件(用于下载到FPGA的配置文件)。

配置采样时钟(Clock):选择合适的时钟频率,确保能够准确捕获信号变化。采样时钟过快或过慢都可能影响信号的显示质量。

设置采样深度(Sample depth):根据调试需求选择合适的采样深度,以平衡资源占用和调试信息的完整性。

选择信号:

在SignalTap界面中,通过双击左侧空白处选择需要监测的信号。

使用Filter功能选择特定时期的信号,如pre-synthesis,以方便查找与RTL代码中的信号名一致的信号。

生成并下载调试文件:

保存SignalTap设置文件。

重新进行综合、布局布线,生成bit文件。

将生成的bit文件和SignalTap调试文件一起下载到FPGA芯片。

开始在线调试:

在SignalTap工具中启动信号捕获,开始在线调试。

示例图片:

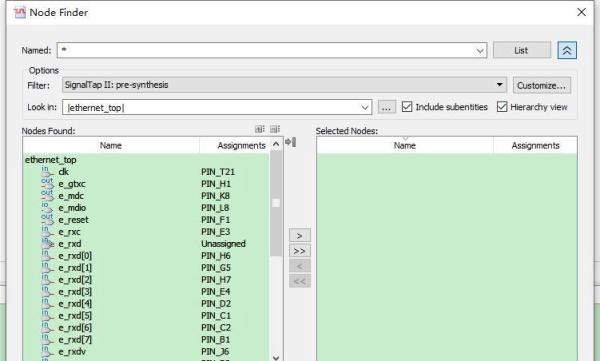

Xilinx Vivado 在线调试方法使用mark_debug

标记信号:

在需要捕获的信号定义语句前添加(* MARK_DEBUG="true" *)标记。

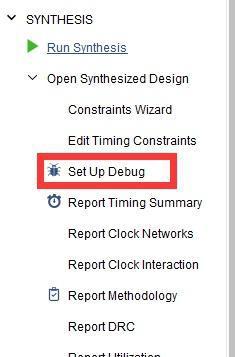

启动调试设置:

在Vivado左侧工具栏中找到并启动调试设置向导。

按照向导提示,选择并配置需要捕获的信号。

指定时钟网络:

确保所有信号都已正确指定合适的时钟网络。

生成调试文件:

根据设置生成调试文件,并检查XDC文件是否保存了最新结果。

下载并调试:

将生成的bit文件和调试文件一起下载到FPGA芯片,开始在线调试。

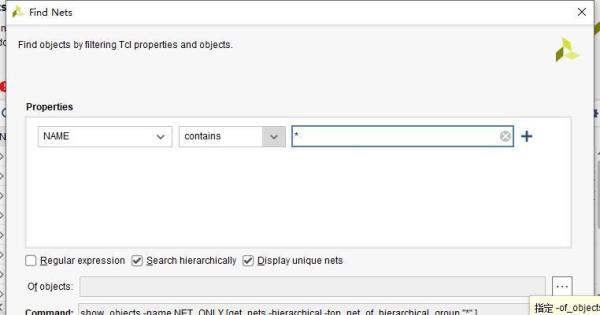

示例图片:

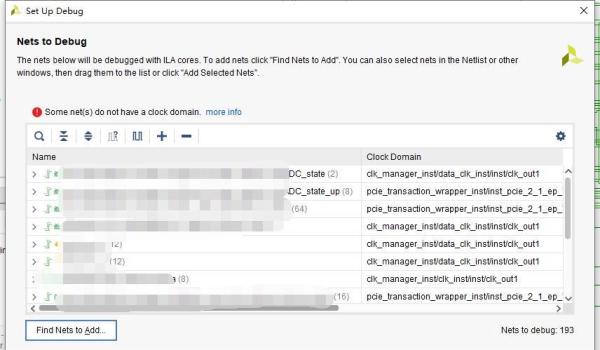

使用ILA IP核

添加ILA IP核:

在Vivado IP Catalog中找到ILA IP核,并添加到设计中。

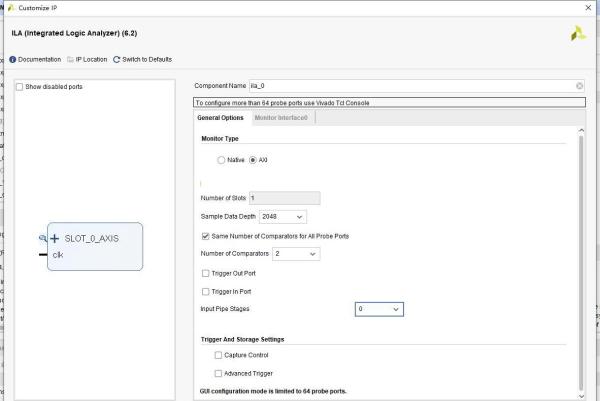

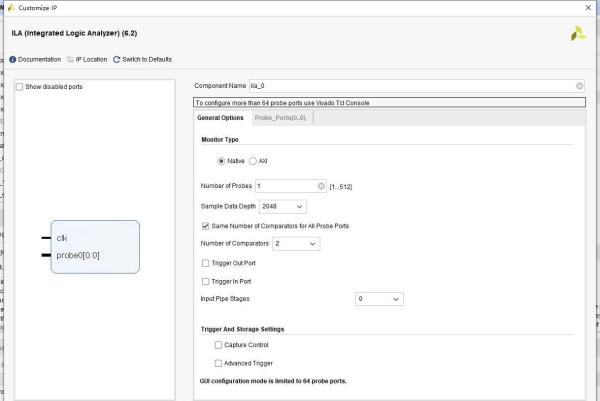

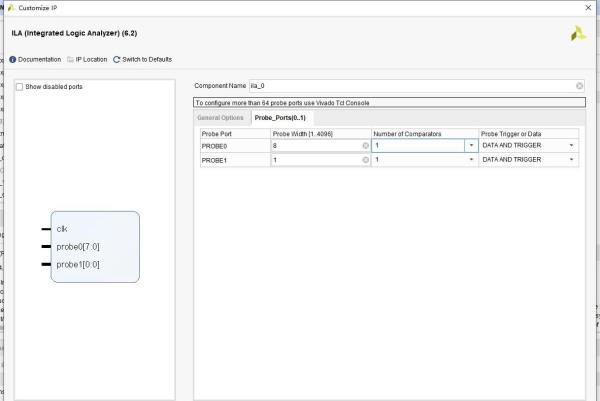

配置ILA IP核:

根据需要选择Monitor Type(如AXI或Native)。

配置信号通道数(Number of Probe)、采样深度(Sample Data Depth)等参数。

如果选择AXI类型,还需配置AXI协议类型、数据位宽、地址位宽等参数。

生成并下载调试文件:

重新进行综合、布局布线,生成bit文件和ILA调试文件。

将生成的bit文件和ILA调试文件一起下载到FPGA芯片。

开始在线调试:

在Vivado调试环境中启动ILA,开始捕获和显示信号。

示例图片:

总结

FPGA的在线调试方法主要包括使用SignalTap(针对Altera Quartus II)和Vivado的mark_debug及ILA IP核(针对Xilinx Vivado)。这些方法允许开发者在硬件实际运行时捕获和显示信号,从而进行电路逻辑的调试和验证。在实际应用中,开发者应根据项目需求和硬件资源选择合适的调试方法,并遵循相应的步骤和注意事项以确保调试的准确性和效率。