时间:2026-02-14 来源:FPGA_UCY 关于我们 0

在高性能网络、数据中心和智能网卡加速领域,硬件与软件协同设计已成为提升网络处理效率的关键。Liberouter 提供的 Network Development Kit(NDK) 就是这样一套专门用来快速开发 FPGA 加速网络应用的开源框架,是连接 高速网络接口、FPGA 逻辑与主机处理器 的工程级利器。

什么是 Liberouter NDK?

NDK 全称 Network Development Kit,是由 Liberouter 研究团队开发的一套框架,用于在 FPGA 加速卡上快速实现高性能网络应用。它并不是一个简单的示例或库,而是一个 可直接用来推进复杂网络硬件开发的平台。

这个套件支持包括 10 GbE、100 GbE 和 400 GbE 在内的高速以太网标准,同时提供了配套的 Linux 驱动、用户态库、示例程序等工具,大幅降低了网络加速 FPGA 设计的门槛。

核心功能和特点

用户应用程序

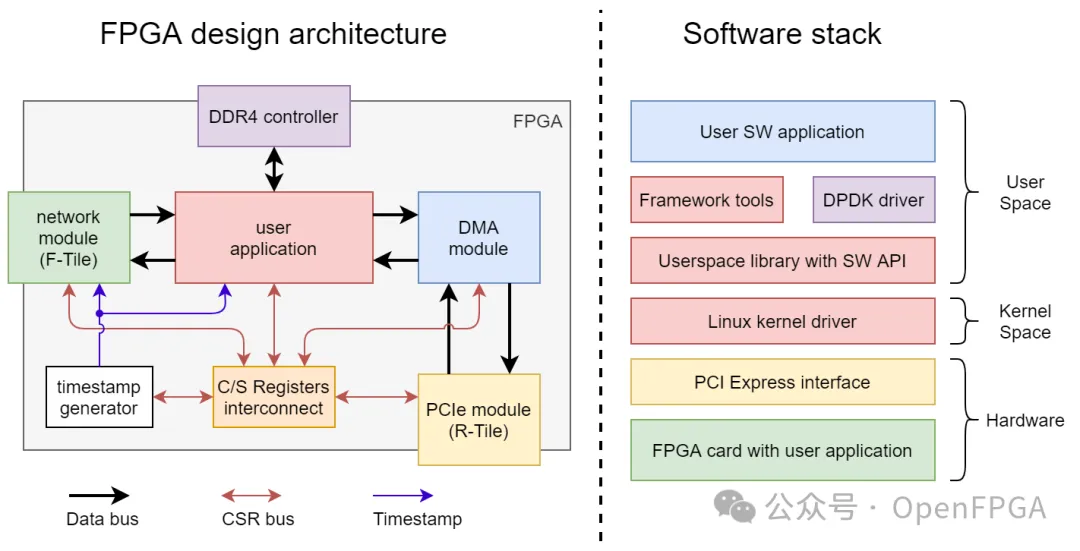

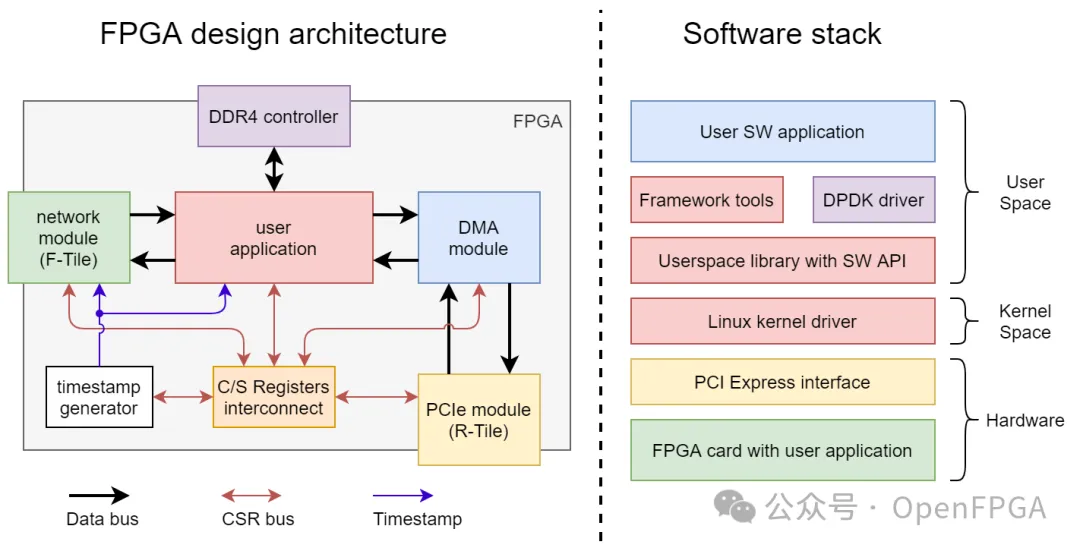

NDK 专为创建具有深度流水线式高速数据包处理的新型网络应用而设计。应用核心是 FPGA 芯片上专用于用户应用的区域,它可以利用 NDK 从网络接口捕获数据包,并通过超高速 DMA 传输将数据发送到主机 CPU。网络模块(NDK 的一部分)负责网络数据包的接收和发送。网络模块通过数据流总线(兼容 AXI4-Stream/Avalon-ST)将接收到的数据包发送到应用核心。然后,同一数据总线用于将数据传输到主机 CPU。整个 NDK 的可扩展性从数十 Gbps 到数百 Gbps 不等。它的设计目标是在每个时钟周期内发送和处理多个数据包。NDK 的标准数据总线经过优化,可以同时传输大量数据包,从而进一步提高吞吐量。上述数据总线包括 MFB (多帧总线)和MVB(多值总线)。就吞吐量而言,几乎唯一的限制是可用的 FPGA 资源。

许多网络应用需要大型数据结构或缓冲区。因此,NDK 提供了一个易于使用的接口,用于与外部存储器(通常是 DRAM)通信。用户可以使用该接口快速开发连接跟踪表、流缓存或数据缓冲区。

在FPGA中实现的用户应用程序可以通过对指定地址范围的读/写请求进行控制。这些请求通过与Intel Avalon-MM兼容的CSR总线从软件传输到应用程序核心。软件用户应用程序可以通过简单的软件API生成这些读/写请求。

超高速DMA传输(DMA Medusa IP)

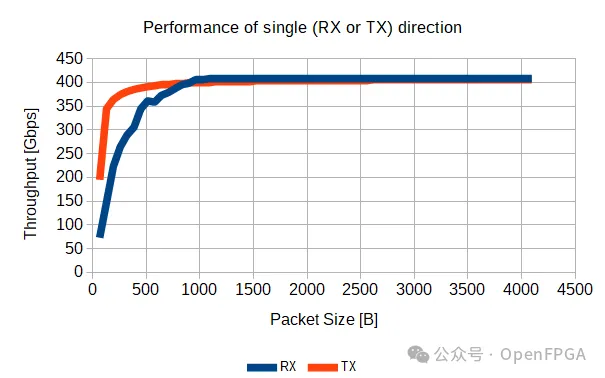

提供与厂商无关的FPGA架构和开源Linux驱动程序,用于采用逐包方式的高速DMA传输。该DMA设计吞吐量为400 Gbps,并采用多通道架构以支持CPU内核间的数据分发。该架构具有高度灵活性,支持各种高端FPGA系列和PCIe总线配置(最高可达PCIe Gen5 x16)。DMA IP可以利用更多PCI端点模块,将吞吐量扩展到100、200和400 Gbps。

已在 Intel Stratix 10 DX 开发套件上演示了 DMA 架构的 400 Gb 吞吐量。然而,同样的 DMA 引擎也能为 Xilinx UltraScale+ 和 Intel Agilex 器件提供极高的吞吐量。NDK Linux 驱动程序允许单独控制所有 DMA 通道。它还提供了一个用户友好的 API,可将应用程序内核直接连接到 DMA IP。此外,还可以通过 DPDK 驱动程序处理 DMA 传输。

示例设计

作为 NDK 的一部分,该项目提供了一个最小化(参考)应用程序的示例设计,该设计可以轻松扩展,为用户应用程序提供硬件加速。该示例设计基于 NDK 框架构建。由于架构设计精良,最小化应用程序核心仅包含连接网络接口和 DMA 模块所需的连接线。此外,最小化示例设计还包含一个用于向 DMA 通道分发数据的单元。

https://cesnet.github.io/ndk-app-minimal/app-minimal.html

实施、验证和运行

上一篇:FPGA基础知识-层次建模的概念

下一篇:FPGA是芯片什么技术?