时间:2025-10-24 来源:FPGA_UCY 关于我们 0

FPGA概述

FPGA,即现场可编程门阵列,是一种在PAL、GAL、EPLD等可编程器件基础上发展而来的技术。它填补了专用集成电路(ASIC)与通用集成电路之间的空白,既保留了定制电路的灵活性,又克服了原有可编程器件在门电路数上的限制。

FPGA简介

FPGA是现场可编程门阵列,通过小型查找表与D触发器实现组合与时序逻辑,具有很高的灵活性。 FPGA通过小型查找表(16×1RAM)来实现组合逻辑功能。每个查找表都连接到一个D触发器的输入端,触发器进而驱动其他逻辑电路或I/O模块。这种结构使得FPGA不仅能够实现组合逻辑,还能实现时序逻辑功能。模块间以及模块与I/O间的连接方式则通过金属连线进行灵活配置。

逻辑功能与结构

FPGA的逻辑功能由其固件决定,独特的模块间连接方式使其实现灵活的逻辑配置。 FPGA的逻辑功能由内部静态存储单元中的编程数据决定。这些存储在存储器单元中的值不仅定义了逻辑单元的行为,还决定了模块间的连接方式以及与I/O模块的交互。

值得一提的是,FPGA的编程过程是可重复的,这意味着用户可以随时根据需求进行修改和优化。

编程技术

市场上的FPGA编程技术包括SRAM、反熔丝与Flash,其中SRAM技术最常用,但需额外支持以保证安全。 SRAM架构应用最广,因其速度快且可重编程。反熔丝FPGA则具有一次编程能力。基于Flash的FPGA是较新技术,同样提供可重编程功能。

值得注意的是,基于SRAM的FPGA可能涉及启动 PROMS支持安全和保密应用的备用电池等额外成本。然而,基于Flash和反熔丝的FPGA则无此隐含成本,有助于降低总系统成本。

FPGA的应用与优势

FPGA技术使得用户无需投片生产,便能设计出合用的ASIC电路。FPGA可作为其他全定制或半定制ASIC电路的中试样片,灵活满足设计需求。 FPGA内部拥有丰富的触发器和I/O引脚,为电路设计提供强大支持。在ASIC电路中,FPGA以其设计周期短、开发费用低、风险小的优势脱颖而出。FPGA采用高速CMOS工艺,功耗低,与CMOS、TTL电平兼容,确保稳定运行。

FPGA的芯片结构

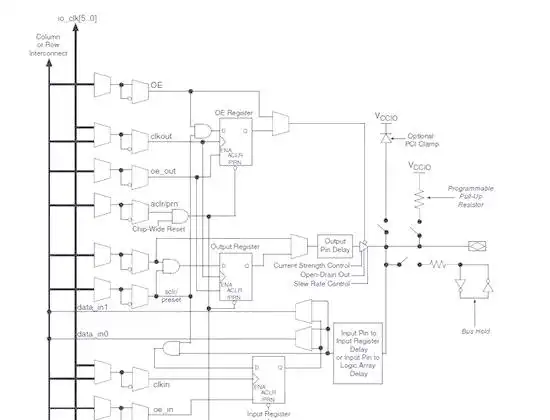

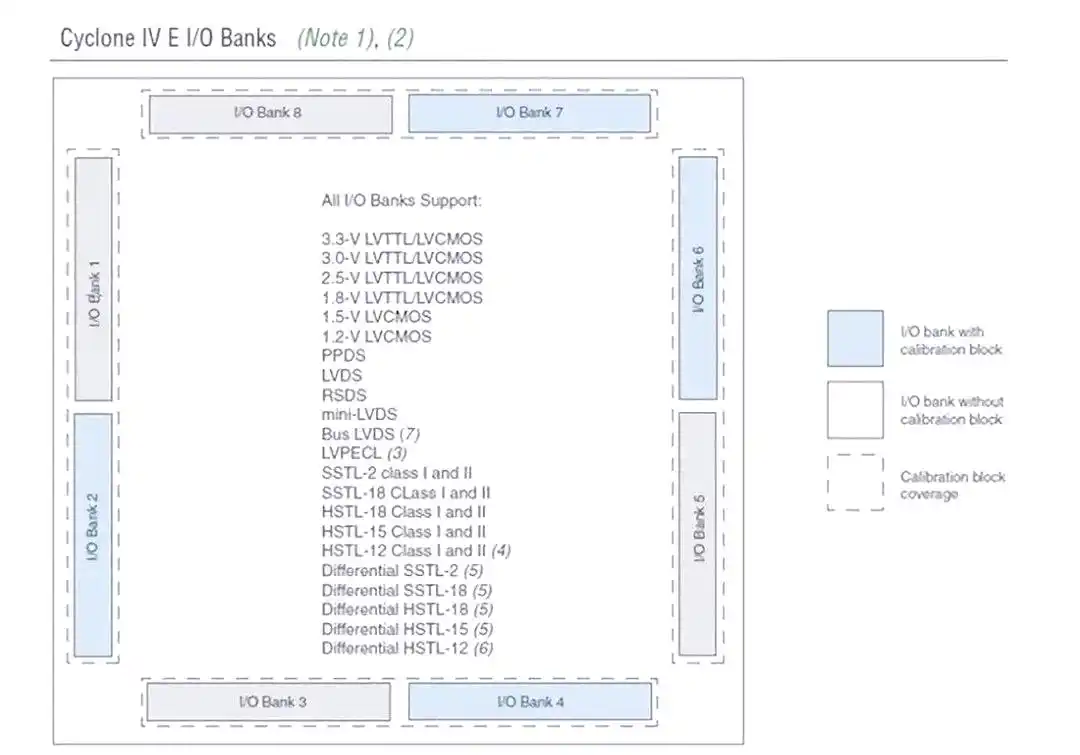

输入输出单元

IOE负责外设连接,针对不同电气特性进行信号匹配与电压转换,是FPGA与外部电路之间的桥梁。 IOE作为FPGA芯片与外部电路的连接桥梁,负责满足在不同电气特性下的输入/输出信号的驱动与匹配需求,涵盖范围广泛,从基础的LVTTL/LVCMOS接口到更复杂的PCI/LVDS/RSDS等差分接口,以及多种电压等级的电平转换。

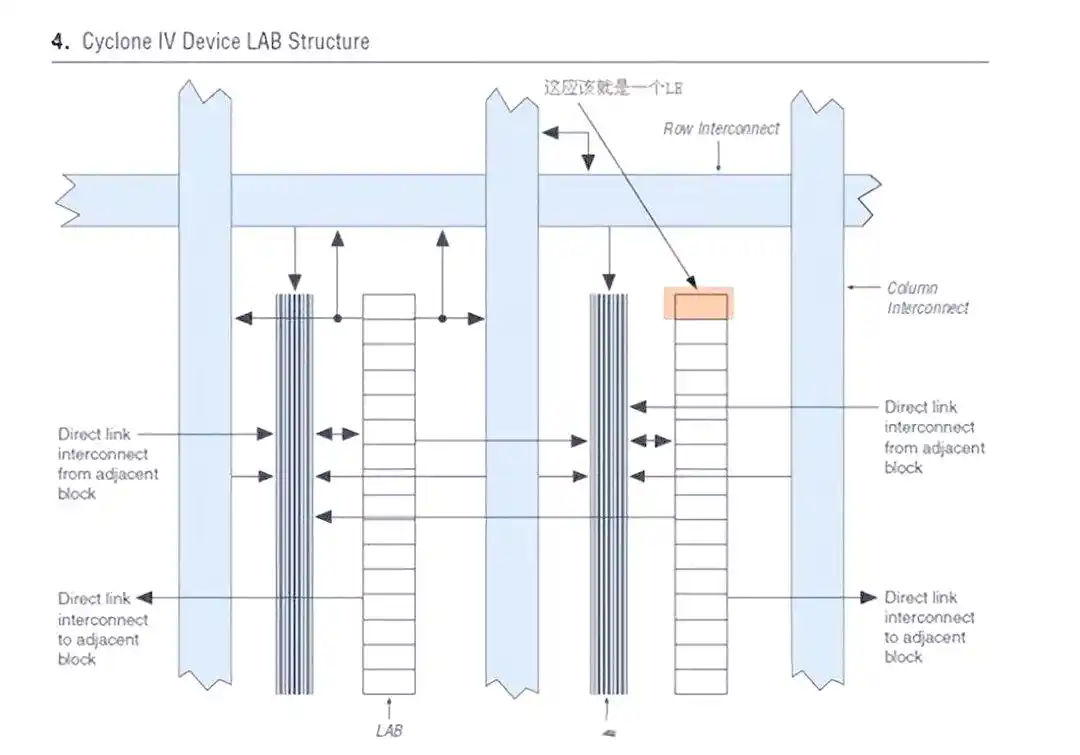

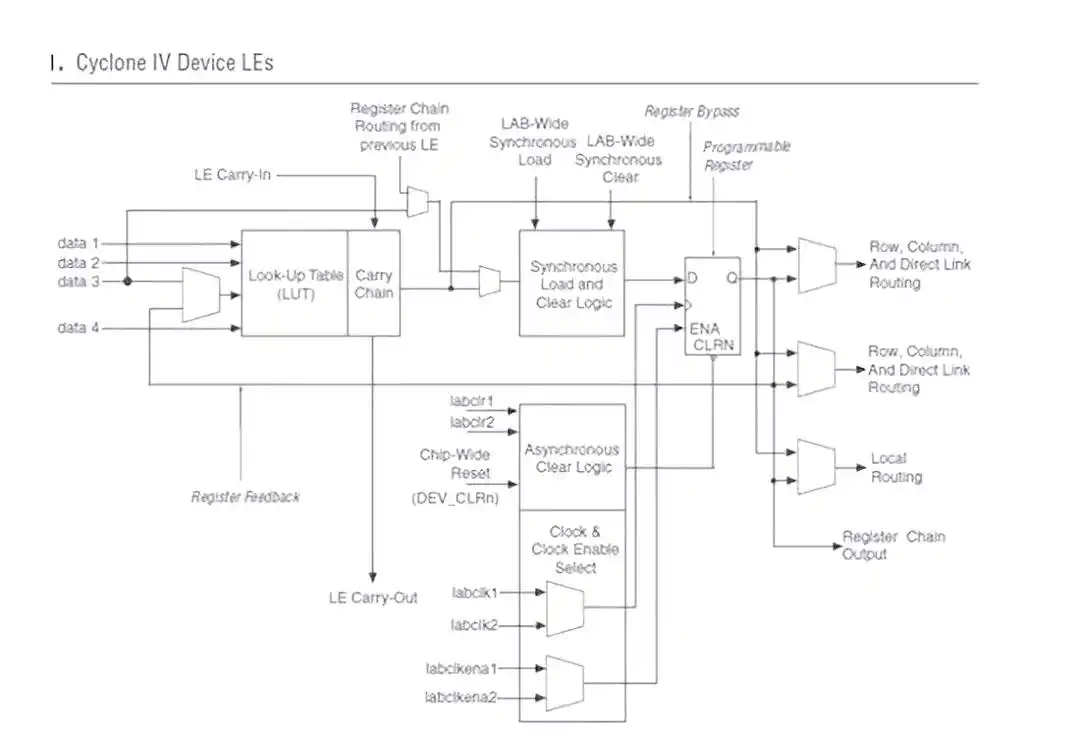

逻辑阵列块

LAB是FPGA的基本逻辑单元,配置不同支持多种逻辑功能,包含查找表与寄存器结构。 LAB作为FPGA的基础逻辑单元,其配置和特性会因器件而异。以EP4CE115F29设备为例,每个LAB的布局包含16个LE(逻辑元素),同时配备了LAB控制信号、LE carry chains、Register chains以及Local interconnect。

LUT(查找表)在FPGA中扮演着至关重要的角色。其核心组件是LUT(查找表),一种类似于静态存储器SRAM的装置。目前,FPGA普遍采用4输入的LUT,这种LUT可以被视为一个拥有4位地址线的16x1 RAM。

内部连接线

FPGA内部的丰富连接线将各个逻辑单元紧密相连,布局布线器根据输入逻辑网表自动选择合适路径。 FPGA内部拥有丰富的连接线,这些连接线将FPGA的各个单元紧密相连。连接线的长度和工艺直接影响着信号在其上的驱动能力和传输速度。布局布线器会依据输入逻辑网表来自动选择合适的连接线,从而连通各个逻辑单元。

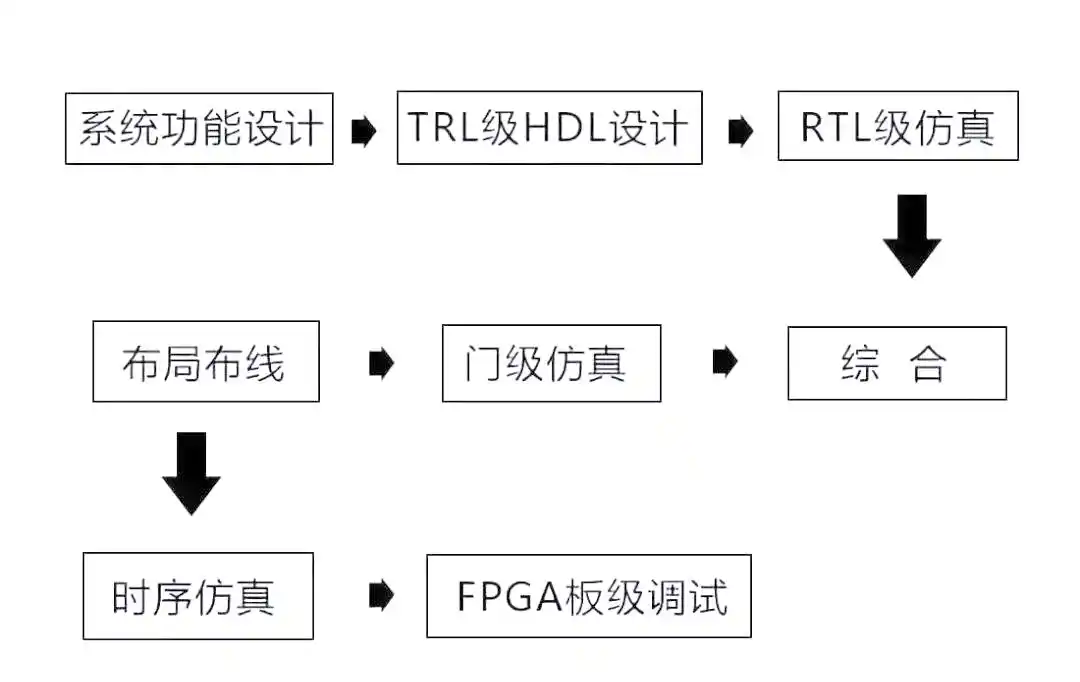

FPGA开发流程

系统功能设计

在设计系统前需进行系统分解与芯片选型,通常采用自顶向下方法进行功能单元划分。 在着手设计FPGA系统之前,必须先完成一系列的准备工作,包括方案论证、整体系统设计以及FPGA芯片的选型。

HDL设计与仿真

RTL级HDL设计,是一种不深入探讨寄存器和组合逻辑细节的设计方法。它专注于描述数据在寄存器间的流动,以及如何控制和处理这些数据流动。RTL级HDL设计法不关注细节,专注于数据流动抽象,需经过功能仿真确认正确性。

综合与布局布线

综合将设计输入转化为低层次逻辑网表,布局布线将其配置到具体芯片上。 综合是将高级抽象层次的描述转化为低层次描述的过程。在综合优化阶段,根据特定目标与要求,对所生成的逻辑连接进行优化,从而将层次设计平面化,为FPGA的布局布线软件提供实现基础。

时序仿真与调试

时序仿真反馈延时信息检测时序违规,FPGA调试需使用逻辑分析仪进行。 时序仿真是一种关键步骤,旨在将布局布线过程中产生的延时信息反馈到设计网表中,从而检测是否存在时序违规现象。在布局布线完成后,时序仿真变得尤为重要。

通过以上各个步骤,FPGA开发能够通过系统化的方法确保设计的正确性与优化。