时间:2025-09-04 来源:FPGA_UCY 关于我们 0

很多时候,人们对于FPGA开发者的印象就是写代码和调试硬件,但其实FPGA工程师有很大一部分时间都在读文档和写文档中度过,客户的需求文档要读,FPGA的器件说明文档要读,参考设计要读,IP核文档要读……

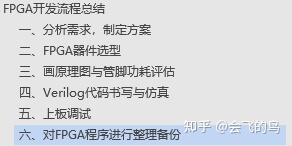

在这里对FPGA的开发流程做一下总结,供FPGA初学者参考。

一、分析需求,制定方案

一些行为都是有目的性的,FPGA开发的目的就是为了满足客户或者领导们提出的“需求”。

就比如一个客户提出mipi一进两出需求,也就是一路mipi输入,两路mipi输出一样的数据。那么FPGA工程师首先就要弄明白mipi是什么,他可以去网上搜,也可以去问更加专业的人,而不是着手就开始写代码,因为他无从下手。

即便工程师明白mipi是用来传输视频的一种协议,并且知道市面上有FPGA现成的方案(例如lattice的Crosslink),但是他也要弄明白这个方案mipi每个lane的带宽满不满足客户的这个需求,有没有可能有更好的方案。

总而言之,个人觉得需求的提出以及方案的确立,是工程师开发中最重要的一环。

二、FPGA器件选型

方案确定之后,就要考虑选型了,这个一个比较复杂的环节,要求工程师对FPGA器件必须非常熟悉。不同的应用场景对选型的侧重点也各有不同,例如消费类产品希望芯片的价格尽量低、封装尽量小、功耗尽量低,而工业类产品一般希望芯片的封装不是BGA的,服务器行业希望芯片的可靠性高。

总结一下,FPGA器件选型一般考虑以下几点:

(1·)芯片的逻辑资源。

一般逻辑资源越多,芯片越贵,所以尽量选择合适大小的芯片。

(2)用户可用IO数量。

同样,IO管脚数量越多,芯片价格也越贵,所以尽量选择合适管脚数量的芯片。

(3)芯片封装。

BGA封装器件一般会比TQFP封装器件的焊接费用要贵,如果pin脚间距在0.5mm以下的话,真实电路板布线还会比较麻烦,所以要根据实际需求取舍。

(4)功耗、价格

功耗这一块,一般便携式设备比较注重。价格这一块,消费类产品比较看重。

三、画原理图与管脚功耗评估

FPGA的整个开发过程,一般需要几个工程师共同完成,FPGA硬件的开发工作一般由硬件工程师来完成,代码工作以及管脚和功耗评估一般由FPGA逻辑工程师来完成。

关于画FPGA原理图,以lattice FPGA为例,一般硬件工程师都会参考相关开发板的原理图,这个原理图可以在lattice官网下载到,如果找不到的话可以问问lattice相关代理商。

原理图画完之后,再对照Hardware Checklist文档检查一下,一般问题就不会很大。(关于引脚分配等资料,在lattice官网也是可以下载到的)

硬件工程师在分配FPGA引脚的可以,虽然可以参考官网下载的pinout信息,但是还是建议FPGA逻辑工程师可以用Diamond开发软件运行一下,看看管脚分配的对不对。

以lattice Crosslink芯片为例,很多时候用户分配好pin脚之后,在lattice Diamond软件上就跑不通,这跟Crosslink芯片内部结构有关系,所以建议硬件工程师分配好管脚之后,能够让逻辑工程师在软件上运行验证一下,然后再画PCB。

关于功耗评估,工程师可以根据实际情况,看需不需要做。一般FPGA开发软件都会提供相关评估方法的。

四、Verilog代码书写与仿真

Verilog代码的书写一般都是FPGA逻辑工程师的工作,少量的代码一般一个逻辑工程师就可以搞定,但是如果代码量太大的话,需要一个高级点的工程师将需求模块化,分给不同的逻辑工程师完成书写。

有些公司甚至要求工程师在写代码之前,将代码的设计思想整理成详细的visio框图,然后大家一个开会讨论这个设计思想是否合理。例如,跨时钟域进行数据交换的时候,大家都会建议你用两个buffer(RAM或fifo)进行乒乓操作。

当然,对于lattice FPGA这种小容量FPGA来说,只要工程师有一定的设计经验,就可以随时进行Verilog代码设计。

Verilog代码书写完毕之后,我们一般都会希望工程师能够进行仿真。仿真的意义在于它能够最大限度的减少Verilog代码的逻辑错误,同时这段时间也是电路板投板的一个时间段,这块做好的话,可以为后面硬件调试节省很多时间。

五、上板调试

FPGA调试阶段,一般是FPGA逻辑工程师和硬件工程师的配合的过程。

(1)拿到板子后,硬件工程师要首先检查板子电源供电。

之所以把这个放在第一条,是因为我不止一次的遇到过,因为电源供电电压不准确,导致FPGA通讯不正常,结果浪费很多时间才定位到这个问题。

(2)下载FPGA程序,查看FPGA是否工作。

怎么说呢,很多情况下第一次总不会成功,要么是硬件电路板某个跟下载有关的FPGA引脚没有拉高,要么是下载线有问题,要么是电路板某个电阻或电容的问题,好好检查一下,一定是硬件连接的问题。

(3)使用JTAG进行在线Debug。

我从未遇到过程序一下载进去,FPGA就能正常工作的情况,所以我们就必须分析错误产生的原因。FPGA硬件调试最重要的一环就是在线Debug(也可以说是在线逻辑分析仪,例如lattice reveal insert工具),它可以直接观测FPGA内部逻辑或引脚的时序逻辑,对我们分析错误有很大帮助。

六、对FPGA程序进行整理备份

作为一个FPGA工程师,我希望大家养成一个程序备份注释的习惯。很多时候,FPGA产品量产之后都会发现一些bug之类的问题,到时候就需要我们工程师重新翻看以前调试好的老程序。如果没有一个很好的备份记录,那将是一个痛苦的过程,你不得不凭借记忆翻找代码,倘若搞混了代码,你还要费时间重新调试程序。如果代码丢了找不到的话,那将是一个悲剧。