时间:2025-08-08 来源:FPGA_UCY 关于我们 0

什么是 FPGA?

Field-Programmable Gate Array 即现场可编程门阵列,作为一种可编程器件,既解决了 ASIC(专用集成电路)的不足,又克服了原有可编程器件门电路数有限的缺点。它集成了大量的原始逻辑资源(触发器、查找表 LUT 和布线),并提供了可配置的 I/O 口及硬 IP(Block RAM、PLL、DSP、通用接口等)依赖工程师采用 HDL(Hardware Description Language,硬件描述语言)进行编码,各个逻辑并行工作来实现指定的功能。它是基于硬件描述的芯片。

为什么 FPGA 可编程?

一提到编程,大家肯定想到的是 coding 的那套软件编程的概念,但 FPGA 的编程是硬件编程,要理解这些需要看 FPGA 的内部结构和工作原理。

一、FPGA 基本结构

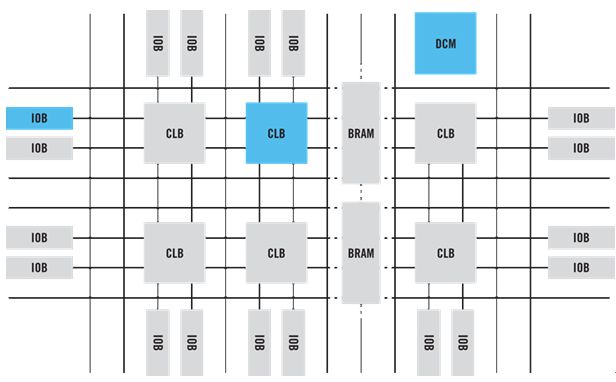

图 1 FPGA 的基本结构

FPGA 内部集成了很多逻辑块(Logic Block),这些逻辑以阵列的形式排布着,散步在各个逻辑块之间的内部互联线(Interconnect),它们就好比 PCB 板上的导线,将 FPGA 内部的各个相关逻辑进行互联,它们的起点和终点都是 IOB(I/O Block),IOB 是 FPGA 和外部器件的物理接口,有丰富的电平接口。

Altera FPGA 片上逻辑主要由 logic Array Blocks(LAB)与 Route 组成,每个 LAB 包含一定数量的 logic Element(LE),LE 可以认为是 FPGA 中最基本的逻辑单元。Route 可以认为是许多连接节点的导线段,这些连接节点不仅用来连接片上逻辑,也用来连接走线本身。

咱们从外往内部说,首先是 IOB,IOB 是芯片与外部电路的物理接口,主要完成不同电气特性下输入/输出信号的驱动与匹配要求,比如从基本的 LVTTL/LVCMOS 接口到 PCI/LVDS/RSDS 甚至各种各样的差分接口,从 5V 兼容到 3.3V/2.5V/1.8V/1.5V 的电平接口,下面是 ALTERA 公司的 Cyclone IV EP4CE115F29 器件的 IOB 结构。

图 2 Cyclone IV EP4CE115F29 器件的 IOB 结构

FPGA 的 IOB 按组分类,每组都能够独立地支持不同的 I/O 标准,通过软件的灵活配置,可匹配不同的电器标准与 IO 物理特性,而且可以调整驱动电流的大小,可以改变上/下拉电阻,Cyclone IV 设备有 8 个 IO blank(组),见下图:

图 3 Cyclone IV 的 IO Bank

然后是 LAB,LAB 是 FPGA 的基本逻辑单元,其实际的数量和特性依据所采用的器件的不同而不同,EP4CE115F29 设备的每个 LAB 的布局包括 16 个 LE、LAB 控制信号、LE carry chains、Register chains 和 Local interconnect,其 LAB 结构图如下:

图 4 Cyclone IV 器件的 LAB 结构

最后是最基本的单元 LE,LE 是 Cyclone IV 设备最小的逻辑单元,每个 LE 主要有 LUT 和寄存器组成的。

图 5 Cyclone IV 器件的 LE

查找表 LUT(Look-Up-Table)其本质是一个静态存储器 SRAM,目前 FPGA 多采用 4 输入的 LUT,每个 LUT 可以看作一个有 4 位地址线的 16×1 的 RAM。当我们通过原理图或 HDL 语言描述了一个逻辑电路后,FPGA 开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入 RAM。这样,在 FPGA 工作时,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

图 6 FPGA 查找表

Interconnect

FPGA 内部连接线很丰富,根据数据手册的描述,主要有图 3 中的 Row interconnect、column interconnect、Direct link interconnect、和 Local interconnect 和 Register chain interconnect(寄存器之间连接的连接线)。

内部连接线联通 FPGA 内部的所有单元,而连线的长度和工艺决定着信号再连接线上的驱动能力和传输速度。在实际开发中,设计者不需要直接选择连接线,布局布线器可自动地根据输入逻辑网表(这由综合生成)的拓扑结构和约束条件选择连接线来连通各个逻辑单元,所以,从本质上来说,布线资源的使用方法和设计的结果有密切和直接的关系。

二、FPGA 工作原理

FPGA 利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个 D 触发器的输入端(见图),触发器再来驱动其他逻辑电路或驱动 I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到 I/O 模块。FPGA 的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与 I/O 间的联接方式,并最终决定了 FPGA 所能实现的功能,FPGA 允许无限次的编程。

知道了 FPGA 的结构和工作原理后再理解为什么 FPGA 能编程就不难了,HDL(Hardware Description Language)之所以叫 Description 而不叫 Design,就是因为工程师用 HDL 语言描述一个功能、一个行为、一个过程,然后在通过 EDA 工具把这种描述语言综合布局布线成实际的硬件电路。可以说 FPGA 编程是设计数字电路,而不是真正意义上的软件编程。HDL 设计输入其实就是电路设计的抽象输入,编译工具的综合就是将这些设计输入翻译成由与、或、非门及 RAM、触发器、寄存器等基本逻辑单元组成的逻辑连接,即网表。这些网表文件作为厂家布局布线工具的输入。

除了上述资源外,FPGA 内部还包含一些嵌入式块 RAM、底层内嵌功能单元(DLL、PLL、DSP 和 CPU 等软核)、硬核(乘法器和串并收发器等)等资源,大大方便了系统级的设计。

三、FPGA 主要应用领域3.1 数据采集和接口逻辑

1)数据采集

低速的 A/D D/A 数据采集可以直接通过 SPI 或 I2C 等方式连接到 MCU 或 DSP 上,但如果是高速的 A/D D/A 转换芯片,如视频的 decoder encoder 不能与通用的处理器直接接口,在这种情况下 FPGA 可以完成数据采集的粘合逻辑功能。 大疆无人机上的视频采集使用了 FPGA。

2)接口和 I/O 扩展

有些实际的应用需要很多 I/O 接口,同时又对速度有一定的要求,这是通过处理器就显得力不从心,而恰恰 FPGA 资源丰富又可编程,就能满足这样的需求。

很多情况下产品需要和 PC 机通信,PC 机的接口丰富,如:PCI、PCIE、USB 等,这样就需要专用的接口芯片,附加的芯片会带来一些 PCB 面积和功耗方面的问题,这些接口逻辑同样可以在 FPGA 内部实现,很多厂商提供一些实现好的 IPcore 可以直接使用。

除了 TTL、COMS 接口电平之外,LVDS、HSTL、GTL/GTL+、SSTL 等新的电平标准逐渐被很多电子产品采用。比如,液晶屏驱动接口一般都是 LVDS 接口,数字 I/O 一般是 LVTTL 电平,DDR SDRAM 电平一般是 HSTL 的。 在这样的混合电平环境里面,如果用传统的电平转换器件实现接口会导致电路复杂性提高。利用 FPGA 支持多电平共存的特性,可以大大简化设计方案,降低设计风险。

3.2 信号处理

无线通信、软件无线电、高清影像编辑和处理等领域,对信号处理所需要的计算量提出了极高的要求。传统的解决方案一般是采用多片 DSP 并联构成多处理器系统来满足需求。但是多处理器系统带来的主要问题是设计复杂度和系统功耗都大幅度提升,系统稳定性受到影响。FPGA 支持并行计算,而且密度和性能都在不断提高,已经可以在很多领域替代传统的多 DSP 解决方案。

3.3 芯片验证

做一些功能性的验证,使得软件和硬件可以同时进行开发。

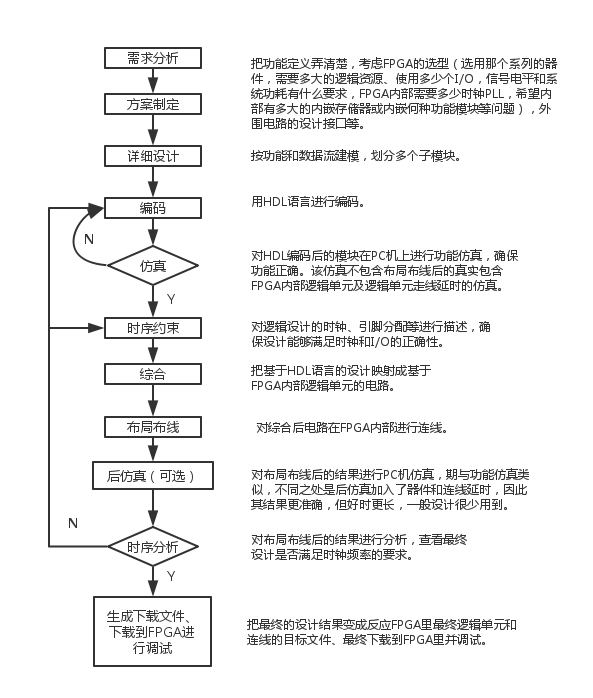

四、FPGA 的开发流程

上一篇:典型FPGA设计开发流程