时间:2025-07-28 来源:FPGA_UCY 关于我们 0

简介:本教程为FPGA初学者提供了一个全面的学习路径,涵盖了从基础知识到实际应用的各个方面。介绍了数字电路基础,FPGA架构和开发工具,详细讲解了设计流程,从设计输入到编程下载的每个步骤。此外,还包括了FPGA在通信协议、图像处理、数字信号处理等领域的应用实例,并鼓励实践操作,从简单的LED控制项目到更复杂的数字信号分析器项目。进阶知识部分则介绍了SoC、HLS以及FPGA在AI领域的应用,旨在帮助学习者为未来的电子设计和研发工作打下坚实基础。

1. FPGA基础知识介绍 1.1 FPGA的定义与发展历程

FPGA(Field-Programmable Gate Array)即现场可编程门阵列,是一种可以通过编程来实现特定逻辑功能的集成电路。与传统的ASIC(Application Specific Integrated Circuit)相比,FPGA在生产后依然可以重新编程,这为硬件设计提供了极大的灵活性。自1985年Xilinx公司发明FPGA以来,这项技术经历了从第一代查找表(LUT)基础的FPGA到如今的具有高级集成度和优化性能的多核SoC FPGA的演进。

1.2 FPGA的主要应用领域

由于其高灵活性和高性能的特性,FPGA被广泛应用于工业控制、通信设备、医疗成像、汽车电子等多个领域。FPGA能够实现高速并行处理,特别适合于需要定制化硬件加速的场合,如视频处理、网络交换、无线信号处理等。此外,随着AI和深度学习的兴起,FPGA因其可重配置性,也成为了机器学习加速器的一个热门选择。

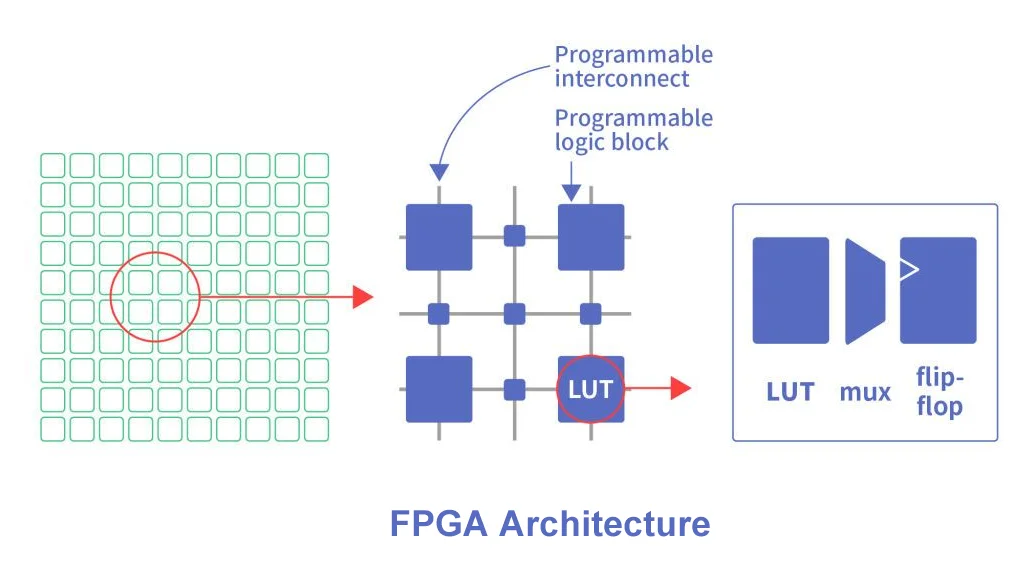

1.3 FPGA的硬件架构概述

FPGA的硬件架构通常由可编程逻辑单元、输入/输出单元(IO)、存储资源和互连网络等组成。逻辑单元可以根据用户定义的逻辑功能配置其内部的查找表和触发器。IO单元负责将内部逻辑与外部信号进行接口。存储资源包括块RAM、寄存器等,为设计提供必要的数据存储。互连网络由可编程的开关和连线组成,实现逻辑单元之间的灵活连接。了解这些基本架构对于深入学习FPGA至关重要。

2. 数字电路概念

数字电路是现代电子设备不可或缺的组成部分,它通过处理离散的数字信号,实现各种逻辑和算术运算。了解其基本概念和设计原则对于掌握FPGA编程和应用至关重要。

2.1 数字电路的基本组成 2.1.1 逻辑门电路的分类和功能

逻辑门电路是数字电路中最基本的组成单元,通过不同的逻辑运算实现复杂的数字功能。根据其功能可以分为以下几类:

这些基本的逻辑门电路可以组合起来形成更加复杂的逻辑运算,为数字电路设计提供了基础。

graph LR

A[输入A] -->|高电平| AND[AND Gate]

B[输入B] -->|高电平| AND

AND -->|输出高电平| OUT[输出]

A -->|高电平| OR[OR Gate]

B -->|低电平| OR

OR -->|输出高电平| OUT

A -->|低电平| NOT[NOT Gate]

NOT -->|输出高电平| OUT

A -->|低电平| NAND[NAND Gate]

B -->|低电平| NAND

NAND -->|输出高电平| OUT

A -->|高电平| NOR[NOR Gate]

B -->|高电平| NOR

NOR -->|输出低电平| OUT

A -->|高电平| XOR[XOR Gate]

B -->|低电平| XOR

XOR -->|输出高电平| OUT

2.1.2 组合逻辑与时序逻辑的区别

数字电路根据功能可以分为组合逻辑电路和时序逻辑电路:

组合逻辑电路通常用于实现算术运算和逻辑运算,而时序逻辑电路则用于记忆和计数,以及更复杂的状态机设计。

2.2 数字电路的设计原则 2.2.1 可靠性设计

可靠性是数字电路设计的一个重要考量,特别是在安全要求高的领域如航空航天和医疗设备中。设计时需要考虑以下几点:

2.2.2 速度与功耗的平衡

在数字电路设计中,通常需要平衡电路的速度和功耗。设计时考虑的因素包括:

电路设计师必须考虑这些原则,以确保设计的电路不仅满足性能要求,还能在实际应用中稳定运行。随着技术的发展,特别是在FPGA平台上,这些设计原则为满足日益增长的性能和功能需求提供了指导。

3. VHDL/Verilog语言学习 3.1 VHDL/Verilog语法基础 3.1.1 数据类型和运算符

在VHDL和Verilog中,数据类型定义了信号或变量在硬件中所表示的数据形式。每种语言有其特有的数据类型和相应的运算符。

VHDL:

VHDL中的基本数据类型包括布尔型(Boolean)、枚举型(Enumeration)和整型(Integer)。在使用中,我们可能会遇到的还有数组(Array)和记录(Record)等复合数据类型。

布尔型使用 true 和 false 来表示逻辑真和假。枚举型可以定义一组命名值,例如:

type state_type is (IDLE, WRITE, READ);

整型通常是使用范围来定义的:

signal counter: integer range 0 to 15;

VHDL的运算符分为算术运算符、关系运算符、逻辑运算符等。例如:

counter := counter + 1; -- 算术运算符

if (counter = 15) then -- 关系运算符

Verilog:

Verilog的数据类型包括线网型(wire)、寄存器型(reg)、整型(integer)等。线网型用作连续赋值语句的左侧变量,而寄存器型用作过程赋值语句的左侧变量。

wire [3:0] a;

reg [3:0] b;

Verilog的运算符包括位运算符、逻辑运算符、算术运算符等,例如:

assign a = b & c; // 位运算符

if (b == 4'b1111) // 关系运算符

3.1.2 信号和变量的声明及使用

在VHDL和Verilog中,信号和变量是用于存储信息的基本单元。

VHDL:

在VHDL中,信号(signal)和变量(variable)的声明和使用有着明确的区别。信号通过 signal 关键字声明,并通过 := 操作符进行赋值,而变量使用 variable 关键字声明,并通过 := 操作符进行赋值。信号的赋值通常在架构(architecture)部分,而变量则在过程(process)或函数(function)内部赋值。

signal my_signal : std_logic;

variable my_variable : integer := 0;

Verilog:

在Verilog中,信号使用 wire 或 reg 等关键字声明。 wire 类型通常用于连续赋值,而 reg 类型用于过程块内的赋值。信号声明后,可以使用赋值语句进行赋值操作。

wire my_signal;

reg my_reg;

3.1.3 信号与变量的初始化

在设计中,合理地初始化信号和变量有助于避免不可预知的错误,并有助于仿真和调试。

VHDL:

在VHDL中,信号默认不会被初始化,但可以在声明时给定初始值。变量则可以在声明时初始化。初始化信号或变量时,应考虑到硬件实现中的约束。

signal my_signal : std_logic := '0'; -- 初始化信号

variable my_variable : integer := 0; -- 初始化变量

Verilog:

在Verilog中,信号和变量都可以通过声明时给定初值。对于线网型(wire)和寄存器型(reg)的声明,可以在声明时直接初始化。

wire my_signal = 1'b0; // 初始化信号

reg my_reg = 0; // 初始化变量

3.2 VHDL/Verilog的结构化设计 3.2.1 实体、架构和配置

在VHDL和Verilog的设计中,实体(entity)和架构(architecture)/模块(module)是构成设计结构的基本单位。配置(configuration)用于指定实体和架构间的连接关系。

VHDL:

VHDL的实体是设计的接口描述部分,定义了与外界交互的端口。架构是实体的具体实现,描述了实体的内部逻辑。

entity my_entity is

port (

a : in std_logic;

b : out std_logic

);

end entity my_entity;

architecture my_arch of my_entity is

begin

-- 描述逻辑

end architecture my_arch;

配置用于指定架构实例和实体实例之间的映射关系。

Verilog:

在Verilog中,模块(module)即代表了一个设计实体,它定义了输入和输出端口,并在模块内部实现逻辑。

module my_module(input a, output b);

// 描述逻辑

endmodule

3.2.2 时序逻辑和组合逻辑的编写方法

VHDL:

时序逻辑通常使用进程(process)来实现,进程内的信号在时钟边沿触发下更新。组合逻辑则不需要进程,直接在架构中描述信号的逻辑表达式。

process(clk)

begin

if clk'event and clk = '1' then

-- 时序逻辑

end if;

end process;

-- 组合逻辑

my_signal <= a and b;

Verilog:

时序逻辑使用 always 块,并根据时钟边沿来触发。组合逻辑则直接在 always 块中描述,且没有敏感列表。

always @(posedge clk) begin

// 时序逻辑

end

always @* begin

// 组合逻辑

end

3.2.3 编写组合逻辑和时序逻辑的注意事项

在编写组合和时序逻辑时,设计者需要注意一些关键点,以避免设计中可能出现的竞态条件(race condition)、毛刺(glitch)或不可预测的行为。

组合逻辑:

时序逻辑:

通过以上对VHDL和Verilog语法基础的深入理解,可以更好地掌握硬件描述语言的使用,为设计复杂的FPGA硬件功能打下坚实的基础。

4. ``` 第四章:FPGA架构详解

在数字电路和逻辑门的知识基础上,进一步深入了解FPGA的架构是极其重要的。FPGA的架构不仅决定了其在不同应用中的性能,而且对于设计的效率和资源利用有着深远的影响。本章将深入探讨FPGA的内部结构、可编程资源,以及这些组成部分如何协同工作以实现复杂设计。

4.1 FPGA的内部结构

FPGA的内部结构非常复杂,但主要由逻辑块、互连资源、输入输出块和可编程I/O单元组成。这些元素共同为FPGA提供了无与伦比的灵活性和功能。

4.1.1 可编程逻辑块(CLB)

CLB是FPGA内部的核心组件之一,它负责实现用户定义的逻辑功能。每个CLB包含一系列可以编程配置为实现特定功能的逻辑元素,例如查找表(LUT)、触发器、多路选择器等。

查找表(LUT)

查找表(LUT)是一种实现组合逻辑的高效方法。LUT的基本工作原理是将输入信号作为地址,利用存储在查找表中的数据来实现对输出信号的快速查找。这种结构非常适合实现任意逻辑函数。

// 示例:Verilog代码实现4输入查找表

reg [3:0] lut[0:15]; // 定义一个16个元素的查找表,每个元素4位宽

always @ (posedge clk) begin

lut[0] <= 4'b0000; // 初始化查找表

lut[1] <= 4'b0001;

lut[2] <= 4'b0010;

...

lut[15] <= 4'b1111;

end

assign output = lut[{a, b, c, d}]; // a, b, c, d为输入信号,组合成查找表的索引

在上述代码中,我们定义了一个查找表并初始化其内容,然后根据输入信号的组合来选择对应的输出。这个过程是由硬件直接实现的,因此可以达到极高的速度。

4.1.2 输入输出块(IOB)

FPGA的输入输出块(IOB)提供灵活的接口用于与外部电路交互。每个IOB包含一系列电路元件,例如输入缓冲器、输出缓冲器、三态控制逻辑等,使得FPGA可以处理多种I/O标准和信号电平。

输入输出缓冲器

输入输出缓冲器允许FPGA与不同电压级别的设备通信,同时保护内部逻辑免受外部电路可能产生的电气噪声和电压尖峰的影响。FPGA通常提供了许多不同类型的缓冲器,以适应特定的应用需求。

// 输入缓冲器示例

module IOB_input (

input wire pad_i, // 外部引脚信号

output reg data_o // 内部数据信号

);

always @ (posedge clk) begin

data_o <= pad_i; // 将外部信号同步到内部时钟域

end

endmodule

在上述代码中,我们展示了一个简单的输入缓冲器模块,它将外部信号同步到内部时钟域,并输出到内部逻辑。

4.2 FPGA的可编程资源

FPGA的可编程资源包括查找表、触发器、寄存器和RAM等,这些资源是实现复杂逻辑和存储功能的基础。

4.2.1 查找表(LUT)

我们已经了解到查找表(LUT)是FPGA中实现组合逻辑的关键组件。为了更好地理解LUT在FPGA中的使用,我们可以绘制一个简化的LUT结构图。

graph TD;

A[输入信号] -->|地址| B[查找表];

B --> C[输出信号];

上述的mermaid流程图展示了查找表的基本工作原理。输入信号作为地址来索引查找表,并得到输出信号。

4.2.2 触发器、寄存器和RAM资源

触发器和寄存器为FPGA提供了存储单个比特信息的能力,而内置的RAM模块则可以存储大量的数据。这些资源对于设计时序逻辑和数据存储至关重要。

触发器的使用

在FPGA设计中,触发器通常用于实现状态机和寄存器等时序电路。每个触发器都可以存储一个二进制位,并根据时钟信号改变其状态。

// Verilog代码实现D触发器

module DFlipFlop (

input wire clk, // 时钟信号

input wire d, // 数据输入

output reg q // 输出

);

always @ (posedge clk) begin

q <= d; // 在时钟上升沿将输入d的值传递到输出q

end

endmodule

以上代码展示了一个简单的D触发器实现,当时钟信号上升沿到来时,输入d的值被传递到输出q。

通过这些可编程资源的深入讨论,我们可以看到FPGA内部架构的灵活性和复杂性,以及如何利用这些组件来设计和实现复杂的数字电路。在后续的章节中,我们将探讨如何使用开发环境和工具来将这些概念应用于实际项目中。

在本章节中,我们从FPGA的内部结构开始,深入理解了可编程逻辑块(CLB)和输入输出块(IOB)的作用和设计原理。接着,我们详细探讨了FPGA的可编程资源,包括查找表(LUT)、触发器、寄存器和RAM。通过实例代码、逻辑分析、mermaid流程图和Verilog代码块,本章节深入解释了FPGA架构中各个组件的具体应用,并为下一章节的开发环境和工具使用打下了坚实的基础。接下来的章节将关注如何利用这些工具将设计从概念转变为实际的FPGA实现。

# 5. 开发环境与工具使用

## 5.1 FPGA开发工具概述

在进行FPGA开发时,选择合适的开发工具是至关重要的。这些工具不仅要帮助设计者高效地进行硬件描述语言编程,还要在设计验证、综合、布局布线、时序分析等环节中提供强大的支持。目前业界最为主流的FPGA开发工具有Xilinx的Vivado和Intel的Quartus Prime。

### 5.1.1 Xilinx Vivado与Intel Quartus的对比

Xilinx Vivado设计套件是针对7系列及以后FPGA的全新设计环境。相较于以往的ISE,Vivado提供了更快速的设计实施、更高的设计容量以及更紧密的集成性。以下是Vivado的一些关键特点:

- **设计流程集成**: Vivado集成了从设计输入到硬件实现的整个流程,极大地提高了设计效率。

- **IP集成**: 提供了大量预制的IP核,可以很方便地集成到设计中,加速开发过程。

- **性能优化**: Vivado提供了综合、实现、分析等一系列工具,帮助设计者优化设计性能。

Intel的Quartus Prime设计软件,对应于Xilinx的Vivado,是针对Intel FPGA的综合开发环境。Quartus Prime同样提供了强大的设计能力,并具有以下特点:

- **用户友好**: Quartus Prime的操作界面直观,易于上手。

- **兼容性**: 支持多种Intel FPGA系列,向下兼容性好。

- **性能分析**: 集成了性能分析和功耗优化工具,有助于设计优化。

### 5.1.2 仿真工具ModelSim和VCS的使用

仿真工具是硬件开发过程中不可或缺的一部分,它可以帮助设计者在实际硬件调试之前发现并修正设计中的错误。

- **ModelSim**: 是Mentor Graphics公司开发的一款广泛使用的仿真软件。它支持多种语言和验证方法,且提供先进的调试工具。ModelSim的仿真速度快,界面直观,非常适合硬件描述语言的仿真工作。

- **VCS**: 是Synopsys公司的产品,广泛应用于ASIC和FPGA的设计验证。VCS支持直接从硬件描述语言生成仿真代码,并且其性能优化做得非常好,尤其适用于大规模的仿真。

对于想要深入了解ModelSim或VCS使用的读者,以下将提供一段示例代码及其操作流程。

```verilog

// Verilog 代码示例:一个简单的计数器模块

module counter(

input clk,

input reset,

output reg [3:0] out

);

always @(posedge clk or posedge reset) begin

if(reset)

out <= 4'd0;

else

out <= out + 1;

end

endmodule

在使用ModelSim进行上述代码的仿真时,通常包括以下步骤:

编写测试平台(testbench)文件,为模块提供输入激励。 在ModelSim中编译设计文件和测试平台文件。 运行仿真,观察波形或控制台输出,验证计数器的行为是否符合预期。 如有必要,修改设计并重复以上步骤直至验证通过。 5.2 FPGA项目管理与编译流程 5.2.1 项目的创建与设置

无论是Vivado还是Quartus,项目创建的初始步骤都相当直观,它们允许设计者指定项目名称、位置、目标FPGA型号以及项目使用的语言等信息。以下是在Vivado中创建一个新项目的步骤概览:

打开Vivado并选择创建一个新项目。 为项目命名并指定存储位置。 选择FPGA设备型号,这将影响后续的设计综合。 选择项目需要包含的源文件类型,例如Verilog或VHDL。 完成向导并打开项目。 5.2.2 设计的综合、布局布线和时序分析

设计的综合、布局布线和时序分析是FPGA开发中的关键步骤,它们直接影响设计的性能和资源消耗。

5.3 FPGA项目优化策略 5.3.1 优化目标与方法

在FPGA项目中,性能优化是一项持续的工作,主要围绕资源占用、功耗和时序三个方面进行。

5.3.2 使用工具进行项目优化

Vivado和Quartus都提供了丰富的工具和功能用于优化设计。

在进行项目优化时,设计者通常需要反复迭代设计,结合综合和布局布线的结果,调整源代码或约束文件,然后重新综合和布线,直到达到预定目标为止。

通过本章节的介绍,我们了解到在FPGA开发过程中选择合适的开发环境和工具的重要性,以及如何管理项目和进行设计的综合、布局布线、时序分析。在后面的章节中,我们将进一步学习如何在设计流程中实现优化,并通过实例加深理解。

6. 设计流程全面解析

设计流程的全面解析是整个FPGA开发中的关键环节,涉及到从设计输入、实现到验证的每一个步骤。一个优秀的FPGA设计流程不仅可以帮助工程师更高效地完成项目,还能确保设计的品质和性能达到预期目标。

6.1 设计输入 6.1.1 从概念到设计的转换

在FPGA设计的早期阶段,工程师需要将设计概念转化为可执行的设计输入。这通常需要对需求进行详细的分析,并将其转化为具体的功能描述。这一过程可能包括需求规格书的编写、功能模块的划分,以及初步的技术选型。

接下来是设计描述的阶段。在这里,设计者将使用HDL语言(如VHDL或Verilog)或高级设计工具来编写代码。这些代码将详细描述每个模块的行为和接口。对高级工程师而言,编写可重用的代码模块是提高开发效率的重要方式,同时也便于后续维护和升级。

代码块示例:

module adder(

input [3:0] a, // 4-bit input a

input [3:0] b, // 4-bit input b

output [4:0] sum // 5-bit output sum

);

assign sum = a + b; // Adding input a and b

endmodule

6.1.2 设计的模块化和重用策略

模块化设计可以提高代码的可读性和可维护性。它还能够通过设计重用来缩短开发周期和降低成本。在FPGA设计中,模块化意味着每个功能模块都是独立的,每个模块都负责完成特定的任务。通过定义清晰的接口,这些模块可以组合在一起,构成完整的系统。

重用策略涉及到在项目之间共享和利用已有的代码库和IP核。IP核是预先设计好的功能模块,它们通常在FPGA开发环境中直接可用。通过重用IP核,可以减少设计时间,缩短上市时间,并提高设计的可靠性和一致性。

6.2 设计实现与验证 6.2.1 逻辑仿真和时序分析

设计实现是将设计输入转换为硬件可实现的形式的过程。在FPGA开发环境中,这通常包括综合和实现两个主要步骤。综合是将HDL代码转换成逻辑元件的过程,而实现则是将逻辑元件映射到FPGA物理资源上的过程。

在综合和实现之前,工程师需要通过逻辑仿真来验证代码的功能正确性。逻辑仿真涉及到使用测试平台对设计进行仿真,确保每个模块按预期工作。除了功能仿真外,时序分析也是必不可少的步骤。时序分析的目的是检查设计中的时序约束,确保设计在运行时能够满足时钟频率和时序要求。

代码块示例:

// Testbench for the adder module

module adder_tb;

reg [3:0] a;

reg [3:0] b;

wire [4:0] sum;

adder uut(

.a(a),

.b(b),

.sum(sum)

);

initial begin

a = 4'b0000; b = 4'b0000;

#10;

a = 4'b0101; b = 4'b0011;

#10;

// Additional test vectors can be added here

end

endmodule

6.2.2 硬件调试和性能优化

在综合和实现后,设计将被下载到FPGA上进行实际硬件测试。硬件调试通常通过JTAG接口和专用调试工具完成。工程师可以通过查看波形、设置断点、单步执行等手段来检查运行时的行为和解决可能存在的问题。

性能优化是设计流程中另一重要的阶段。性能优化通常包括减少资源的使用和提高运行速度。优化可能涉及到修改HDL代码,调整综合约束,或直接修改综合后的网表。这些步骤需要工程师根据综合和时序分析的结果进行判断和决策。

6.3 设计迭代与优化 6.3.1 从验证到优化的反馈循环

设计流程通常是一个迭代的过程。在每个迭代中,工程师会根据验证的结果进行设计修改和性能优化,直到满足所有设计规格为止。这个反馈循环是保证设计成功的关键。

在完成硬件调试和性能优化之后,如果发现设计不能满足要求,可能需要回到设计输入阶段,重新定义需求或调整设计架构。这个过程可能会重复多次,直到最终的FPGA设计既满足功能需求,又达到性能目标。

6.3.2 功耗和资源的优化技巧

功耗和资源优化是FPGA设计中越来越重要的考量。随着FPGA技术的发展,芯片集成度越来越高,功耗和资源使用成为了设计的瓶颈之一。

优化技巧包括但不限于逻辑优化、时钟树的优化、资源共享、模块化和流水线设计。逻辑优化可能涉及重写代码以减少逻辑门的数量。时钟树优化可以通过合理设计时钟网络来降低功耗。资源共享是指在满足时序要求的前提下,多个模块共用相同的逻辑资源。模块化和流水线设计则可以提高数据处理的吞吐量,减少资源的空闲时间。

通过这些优化方法,工程师可以有效地提升FPGA设计的性能和效率,以满足日益增长的应用需求。

7. FPGA应用实例讲解

FPGA的应用领域非常广泛,从数字信号处理到高速通信,再到现代AI加速,它在每个领域中都有独特的表现。在本章中,我们将探讨FPGA在数字信号处理(DSP)和通信领域的具体应用,并通过案例分析深入了解其工作原理。

7.1 数字信号处理(DSP)应用

数字信号处理是FPGA应用的一个重要方向。FPGA的并行处理能力和灵活的可重构特性使得其在处理复杂的DSP算法时具有显著优势。

7.1.1 常见DSP功能的FPGA实现

FPGA实现DSP功能通常涉及以下几个步骤:

信号采集 :使用ADC(模数转换器)将模拟信号转换为数字信号,以便FPGA处理。 信号处理 :通过算法如FFT(快速傅里叶变换)、FIR/IIR滤波器、DCT(离散余弦变换)等对数字信号进行分析和修改。 信号输出 :将处理后的数字信号转换回模拟信号输出,或者直接输出数字信号到其他设备。 7.1.2 实时信号处理案例分析

以FFT为例,下面的代码展示了如何使用Verilog实现一个简单的FFT处理器:

module fft_engine(

input wire clk, // 时钟信号

input wire rst_n, // 同步复位信号,低电平有效

input wire start, // 开始处理信号

input wire [15:0] real_in, // 输入信号实部

input wire [15:0] imag_in, // 输入信号虚部

output reg [15:0] real_out, // 输出信号实部

output reg [15:0] imag_out, // 输出信号虚部

output reg done // 处理完成信号

);

// FFT模块的内部参数和状态定义

// ...

// FFT处理流程

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

// 异步复位逻辑

// ...

end else begin

if (start) begin

// FFT计算开始

// ...

end

end

end

// 控制FFT计算的完成和输出

always @(posedge clk) begin

if (条件) begin

real_out <= 结果实部;

imag_out <= 结果虚部;

done <= 1'b1;

end else begin

done <= 1'b0;

end

end

endmodule

在实际应用中,FFT处理器模块会通过一系列的运算单元实现快速傅里叶变换算法。此过程需要处理信号的实部和虚部,并将最终结果输出。代码中的"FFT模块的内部参数和状态定义"部分和条件判断逻辑需要根据实际FFT算法来设计。

7.2 FPGA在通信领域的应用

FPGA在通信领域的应用几乎与DSP同样重要,特别是在需要处理高速数据流和自定义协议的场景。

7.2.1 无线通信系统中的FPGA角色

在无线通信系统中,FPGA可以用于实现多种功能,例如:

7.2.2 5G技术中FPGA的应用实例

5G技术推动了通信速率和容量的飞跃,FPGA在其中扮演了核心角色。一个典型的例子是使用FPGA实现大规模MIMO(多输入多输出)技术,这在5G基站中有广泛应用。

大规模MIMO技术通过大量的天线和复杂的信号处理技术,可以大幅度提升无线通信的数据吞吐量和信号质量。在FPGA中,可以设计多通道数据流处理模块,每个模块负责一组天线的信号处理。这需要高度并行和定制化的逻辑电路设计。

FPGA在通信领域应用实例的深入理解,可以透过研究实际案例,结合其快速原型和迭代的优势,不断优化性能和功耗指标。

通过这些应用实例的讲解,我们可以看到FPGA的强大能力和潜力,在现代电子系统设计中的重要地位。在接下来的章节中,我们将进入项目实践指导,为您展示如何在实验板上操作和实现这些高级功能。

简介:本教程为FPGA初学者提供了一个全面的学习路径,涵盖了从基础知识到实际应用的各个方面。介绍了数字电路基础,FPGA架构和开发工具,详细讲解了设计流程,从设计输入到编程下载的每个步骤。此外,还包括了FPGA在通信协议、图像处理、数字信号处理等领域的应用实例,并鼓励实践操作,从简单的LED控制项目到更复杂的数字信号分析器项目。进阶知识部分则介绍了SoC、HLS以及FPGA在AI领域的应用,旨在帮助学习者为未来的电子设计和研发工作打下坚实基础。

上一篇:国产FPGA,走到哪一步了?