时间:2025-03-08 来源:FPGA_UCY 关于我们 0

在传统的FPGA设计流程中,一般是自顶向下的模块化设计,这些模块包括用户自己编写的RTL或者是供应商提供的IP核。而在新推出的高生产力设计流程中是以IP为核心的,把所有的模块都看做是IP,封装为IP,最主要的是IP的设计是基于C语言的,最后通过HLS将C语言代码转化为RTL,这能极大的加快设计进程。从这段时间的学习来看,HLS综合出来的电路比我自己写的RTL更省资源,在时序方面可能会差一些,因为我自己是习惯性的全流水,但它也满足了时序的要求。HLS还提供了非常多的经过深度优化的库,所以我个人觉得HLS综合的电路已经比很多刚接触FPGA不久的工程师要好了,传统的RTL设计可能不会消失,但很可能会越来越少了。

HLS在不添加任何优化指令的情况下默认综合电路为最节省资源的情况,即能使用分时复用就使用分时复用,能在一个周期中完成多个操作(满足时钟频率约束的要求)则绝不流水。从这里得到的启发是,设计不要过度的流水,只要能满足时钟频率的需求,我们在一个时钟周期内可以进行多个操作,于是在低频率的系统中,我们可以节省很多的寄存器资源。这样做还有一个好处是我们可以使用来完成逻辑设计,然后再对输出进行寄存,可以极大的减少代码量,增加代码的可读性,HLS综合后的RTL代码的风格就是这样的,当然因为命名的原因该代码几乎没有可读性,我们可以不用刻意去读懂它。

在学习 HLS工具之前,我们需要了解HLS工具在FPGA开发流程中的作用。工具的设计理念是以IP为核心的,所有的功能模块都可以看做并且封装成一个IP,最后由集成,以实现最大化的设计复用。所以 HLS可以看做是一个IP封装工具,它封装的是由C、C++、或者等高级语言实现的功能函数。

1、写一下我自己理解的 HLS工具学习流程:

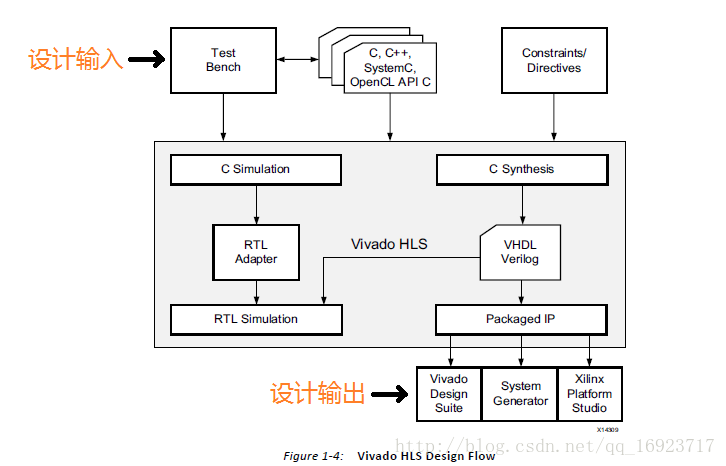

2、从一张图简单讲一下 HLS的设计流程

这张图是用户指南ug902中的,从图中我们可以看到HLS的设计流程可以分为3个大的部分

(1)、设计输入里有三个文件是我们需要手动编写的,、C函数文件、头文件,而文件是在创建工程的时候完成的,主要是器件和时钟频率的约束,就是优化指令文件,一般是C仿真通过之后添加的,这是综合之前的关键一步,后面会联合综合部分讲到。的文档里特别强调了C 的作用,建议不要越过这一步直接综合,HLS一个很大的优越性就是C仿真的速度要比RTL仿真的速度快很多。C函数文件其实对应的就是我们平常编写的RTL,可以把它看成是一个带输入输出端口的盒子,这个盒子完成我们需求的函数功能。而头文件的作用主要是增加代码的可读性和可移植性,头文件里声明任意精度类型,编写宏控制设计的仿真和综合流程。

(2)、仿真综合主要包括两个部分,一是C仿真和C联合RTL仿真,二是C的综合。因为只是为了验证设计的功能正确性,C仿真和C联合RTL仿真较为简单,如果设计没有错误的话,点两下按钮就可以结束了,如果报错,则根据报错信息进行debug就可以了。而C的综合难度较大一点,需要深入了解for循环、数组等结构在不同优化指令下的综合情况,需要看懂综合报告,这就要求对FPGA的底层有一定的了解,如果综合报告没有满足我们的需求,就要修改并重新综合,甚至需要修改C代码,这是一个迭代的过程。当综合报告满足我们的需求并且C和RTL联合仿真通过后就可以进行设计输出了。

(3)、设计输出就没什么 了,根据自己需要将该IP用到的地方进行导出就可以了。

3、设计步骤: 创建工程,编写设计输入 ——参考资料:ug871,仿真和debug ——————-参考资料:ug871,综合及结果分析—————-参考资料:ug871,联合RTL仿真 ——————-参考资料:ug871,ug902输出———————————-参考资料:ug871,ug902

4、再提一下HLS的一个好处:可以通过来将同样的代码综合成不同结构的电路

比如我们要重复使用一个模块A,我们可能在资源不够的时候需要对A进行分时复用,在需要高吞吐量的时候又需要对A进行逻辑复制,如果是写RTL代码的话,这两种方式都需要不少的代码量,并且从一种方式换到另一种方式的时候需要重新编写代码,非常耗时。而使用HLS的话,我们只需要一个for循环对A进行调用就可以了,代码非常少,至于我们需要综合成何种结构的电路则添加不同的就可以了,并且可以同时生成不同的,同时综合成几种不同的电路,非常方便。

5、学习资料

官方论坛里整理的学习资料

%E4%B8%93%E5%8C%BA/-HLS%E5%AD%A6%E4%B9%A0%E8%B5%84%E6%96%99/td-p/

推荐高亚军老师的视频教程:《跟着 SAE学HLS》

6、好的HLS设计 = Good + Good