时间:2025-02-06 来源:FPGA_UCY 关于我们 0

目前,绝大部分的FPGA的IP或者功能都是使用硬件描述语言进行开发的。在目前的人工智能时代,许多的复杂算法、高深的算法,使用硬件描述语言已经无法进行快速的迭代了。因此,利用成熟的语言,进行算法的开发,并利用一些工具或者手段,将其转换为硬件描述语言的IP Core,便成为了一种选择。其中,使用高级设计语言(C/C++)进行FPGA的开发,就称之为高层次综合设计,简称HLS。

本文的目的,在于简单描述如何使用C/C++进行FPGA的IP Core的开发,主要分为2部分:

1.工具和环境以及初级入门

2.高阶应用以及优化

其中,第二部分将另开篇章进行描述。

本文选择的是Intel的工具集,进行开发。

一、环境以及工具集

Intel HLS需要和C/C++编译器,目前支持开源的GCC编译器,以及平台的 (= 4.85

: 18.1 lite (本文安装于/opt//18.1)

: For Intel FPGA 10.5b (Free版本,本文安装于/opt//18.1//)

二、基本使用

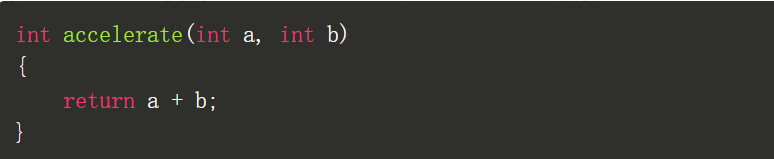

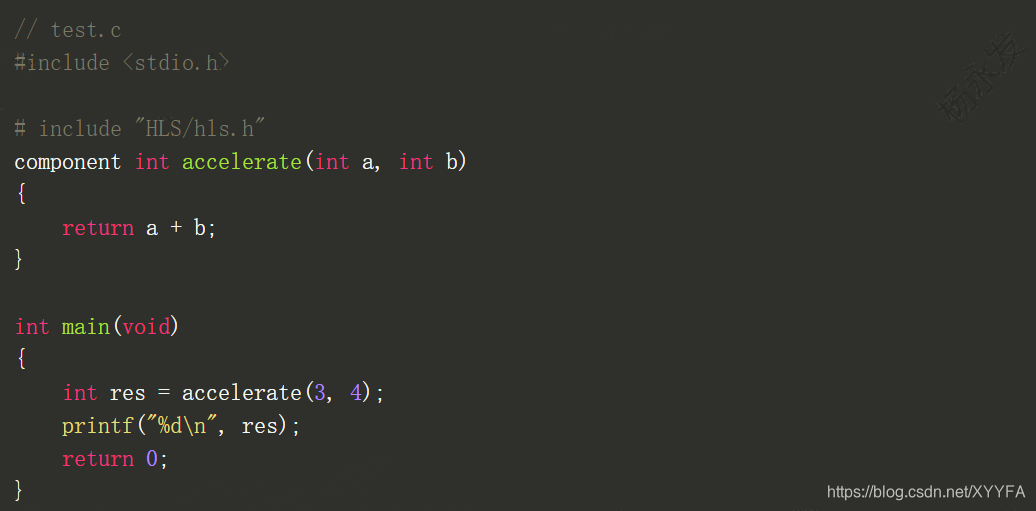

HLS的基本使用与标准的C一模一样,不同的仅仅是编译方式上,以及头文件上。

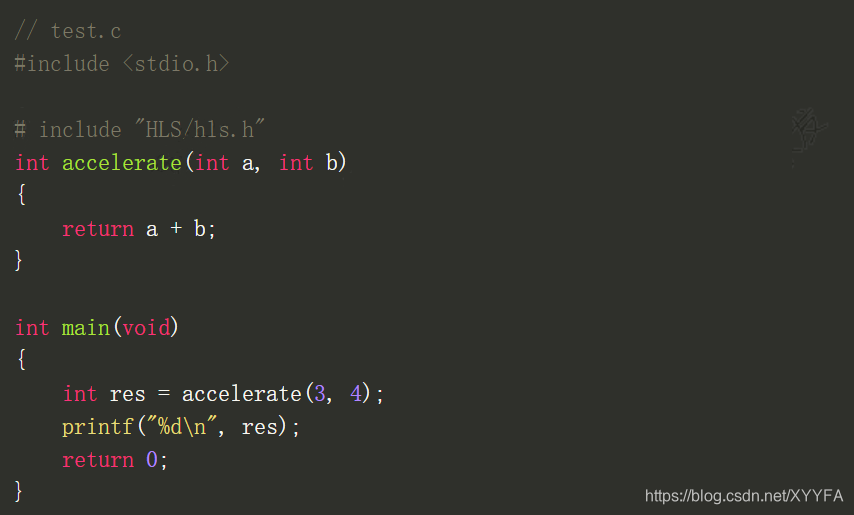

如果是按照C语言的编译方式,则只需要通过GCC即可。我们简单的将上述的代码修改一下,加入HLS的头文件,并选择使用HLS的编译器进行编译。

编译之前,需要指定的路径:功能仿真需要使用,并且需要其提供的一系列库文件。

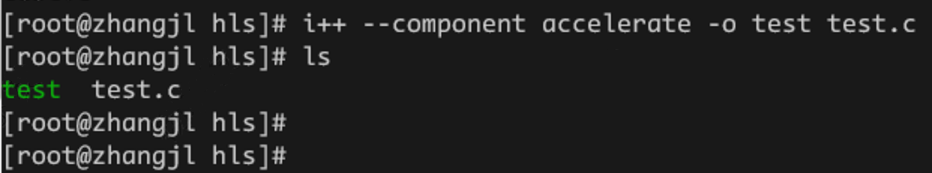

编译的指令是将GCC替换为i++,除此之外就是添加一个新的参数—即可。

编译之后的结果,如下:

生成的test文件同样可以直接运行,只是,生成的只有在CPU端能够运行的文件,并没有生成FPGA端的代码。而我们真正需要的,是在FPGA端的代码。

因此,需要添加新的参数进行编译。

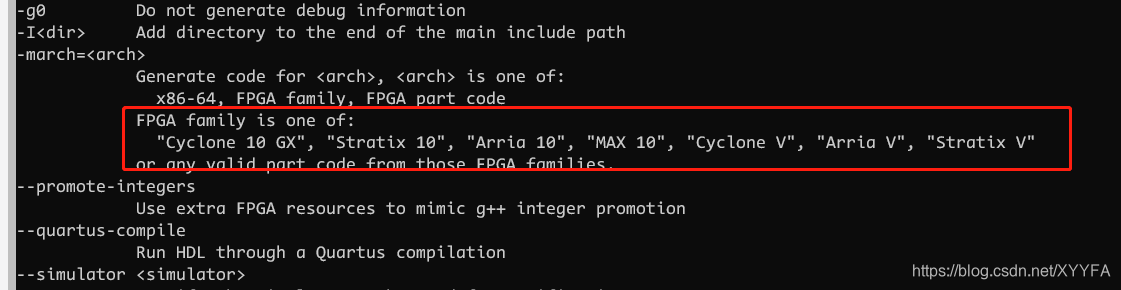

可用的编译指令如下:

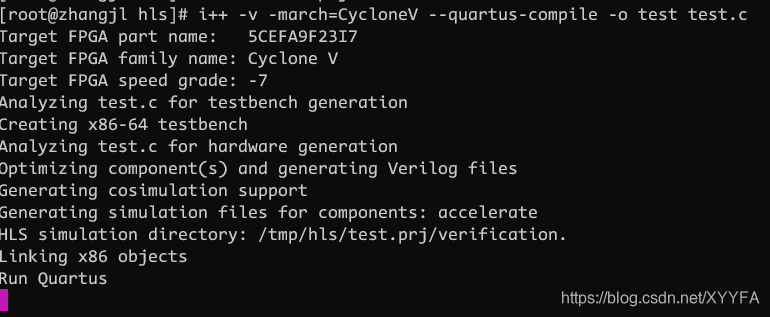

注意,在这里,我们新加了一个参数,-march=,表示,在编译时,按照的器件(FPGA芯片)的资源和电路结构进行编译。

而当前版本的(i++)支持哪些版本的FPGA芯片(器件),则可以根据i++ —help查看。

将对应的名称去除空格,进行替换即可。

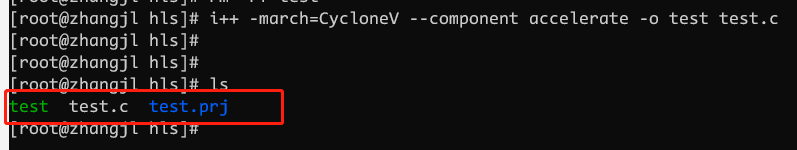

编译之后的结果如下:

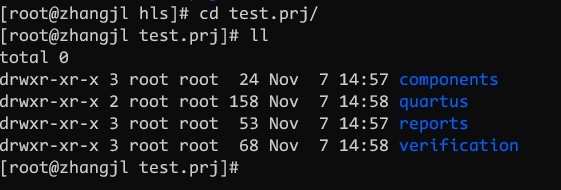

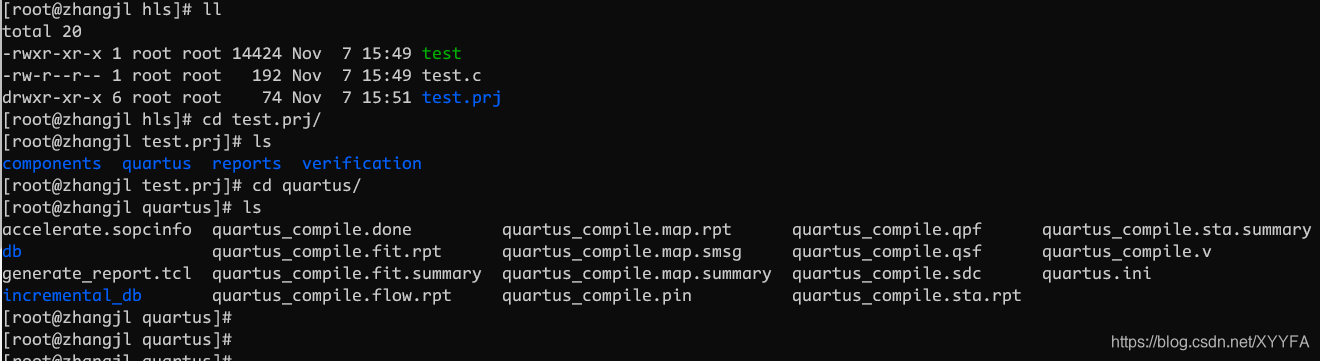

其中,test.prj文件夹当中的文件,就是我们所需要的FPGA端的代码。

为生成的模块代码(即函数所对应的硬件描述语言代码)。

为硬件工程。

为编译结果报告,包括了性能描述报告。性能报告非常重要,在后期的优化当中,优化的主要依据就是借助编译报告完成的则是生成的测试文件。

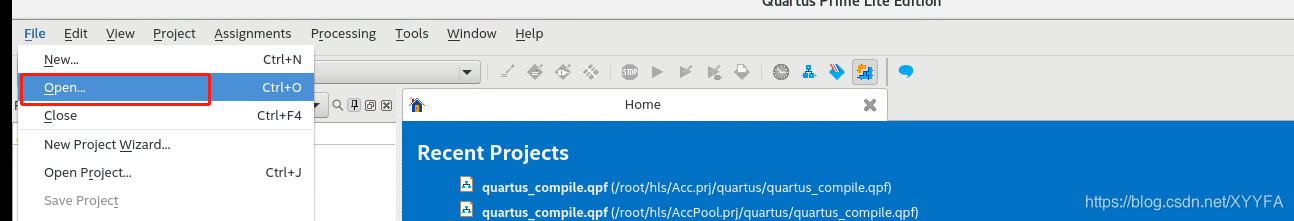

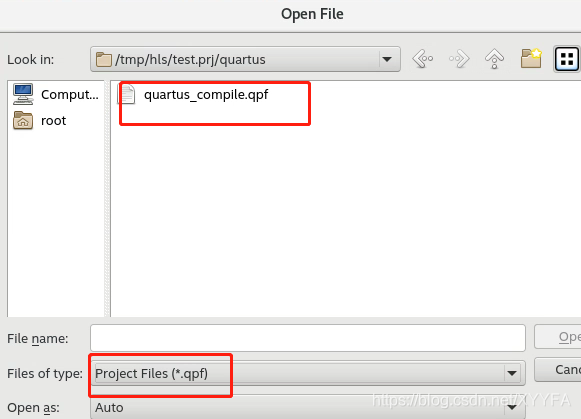

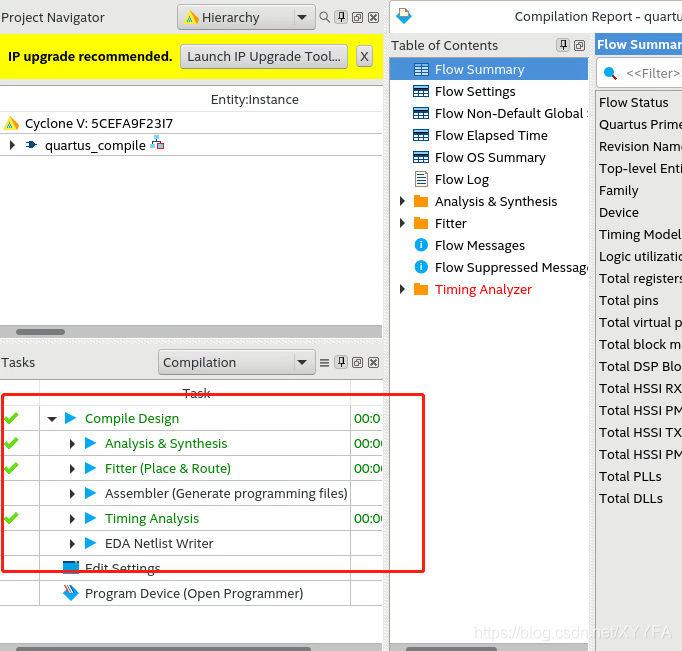

剩下的,就是使用软件,对生成的硬件描述语言代码进行编译,生成FPGA可以使用的文件。

到此,基本的HLS开发就算完成了。但是还是有不少的地方可以进行改进。

三、改进

虽然在编译的时候,我们可以使用—参数指定需要编译生成的模块,但是,如果模块太多,则会导致比较麻烦,因此,我们可以采用另外的方式进行。

如上代码,只需要在函数前面,加上关键字,编译的时候,就可以取消—参数。

上述代码的编译指令修改如下:

得到的结果和之前的一样。

如果不想手动打开进行生成的硬件代码的编译工作,可以在参数当中添加—-参数,当硬件代码生成之后,自动进行工程的编译。

如果需要查看更加详细的编译信息,还可以加上参数-v,如下:

根据我们的修修补补,基本上,最后生成的文件如下:

四、限制

从上面的结果看,我们就已经完成了使用C/C++等高级语言开发FPGA模块的工作,不过,需要澄清的是,我们完成的仅仅是一个模块,并不是整个FPGA工程,因此,这些生成好的代码需要由硬件工程师嵌入到对应的硬件工程当中进行使用;另外,虽然高级语言进行IP Core的开发确实效率比较高,但是,也存在一些限制。

1.main函数不能添加关键字,即main函数不能被编译为FPGA的一个模块。

2.标记为的函数当中,不能使用内存分配函数,包括open,,,free等等。

函数当中不能使用多线程,文件读写等一切关于涉及到系统调用的函数。

上一篇:深度学习模型在FPGA上的部署

下一篇:《FPGA基础知识》课件.ppt