时间:2026-04-15 来源:FPGA_UCY 关于我们 0

1.2 阵列与互连结构 The Array and Interconnect

通过查找表(LUT)和D触发器,可定义其上的逻辑层级——FPGA中的逻辑块(logic block)或功能块(function block)。在单个逻辑块层面,已了解FPGA如何执行计算,后续将重点探讨如何在FPGA结构中布局这些逻辑块并实现互连。

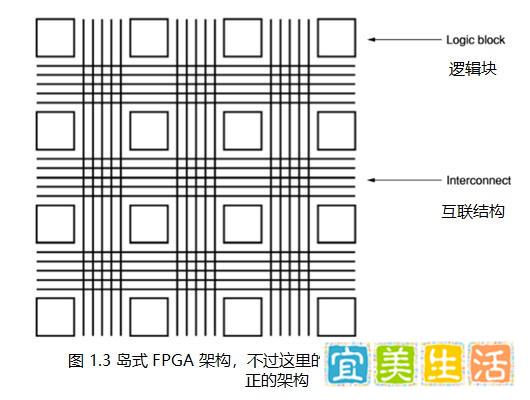

当前主流FPGA实现采用岛式架构(island-style architecture)。如图1.3所示,逻辑块以二维阵列形式平铺,并通过特定方式互连,逻辑块如同“漂浮”在互连网络中的岛屿。

在此阵列结构中,计算任务分布于整个FPGA空间。大型计算被分解为以4-LUT为单位的模块,并映射至阵列中的物理逻辑块。通过配置互连结构,信号可在逻辑块间正确路由。理论上,只要逻辑块数量充足,FPGA可实现任意计算任务。

1.2.1 互联架构 Interconnect Structures

图1.3未完整展示全部互连结构,且所示结构仅为示例,不代表实际FPGA设计。本节将介绍当前FPGA中常见的互连结构,从局部互连扩展至全局互连,以理解不同类型互连的需求。首先从最简单的最近邻通信开始分析。

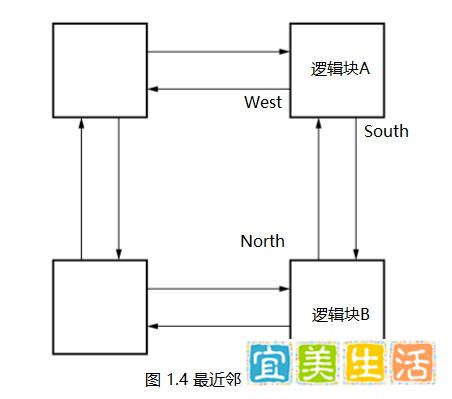

最近邻结构 Nearest neighbor最近邻通信的结构如其名称所示简单。如图1.4所示,在2×2逻辑块阵列中,每个逻辑块仅需通过北、南、东、西四个方向的输入/输出端口与相邻逻辑块通信。

图1.4展示了最简单的路由体系结构示例。尽管看似落后,但此类结构曾用于部分已淘汰的商用FPGA。即使在此简单方案中,仍存在显著的延迟和连接性问题。例如,在1024×1024阵列中,信号延迟与传输距离呈线性关系,因信号需经过多个逻辑块和交换结构才能到达目的地。

从连接性角度看,近邻结构中信号无法绕过路由结构中的逻辑块,每个信号跳数均需经过一个逻辑块。此外,每个方向仅有一个双向信号对,限制了通过逻辑块的信号数量。路由信号与逻辑块自身信号无法并行处理。

由于这些局限性,最近邻结构很少单独使用,但几乎所有当前FPGA结构均包含此类结构,并与其他技术结合以改善其局限性。

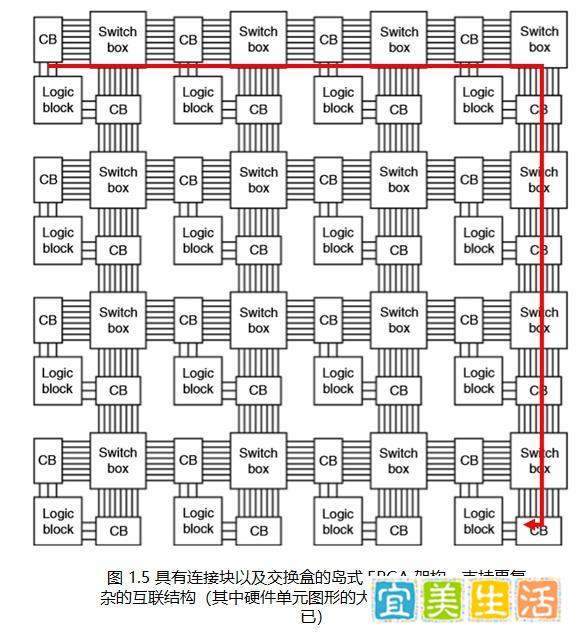

分段结构 Segmented随着互连结构复杂性的增加,硬件单元不再局限于逻辑块。当前大多数FPGA架构更接近图1.5,包含逻辑块以外的硬件单元。

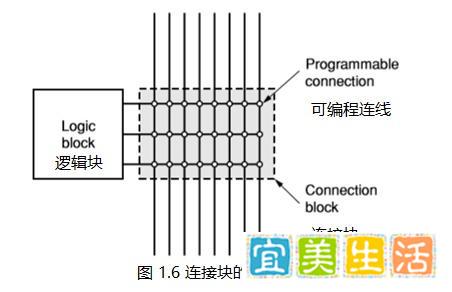

图1.5中引入了连接块(Connect block)和交换盒(Switch box/block)两种硬件单元。路由结构更具通用性,呈现网状(mesh-like)特征。逻辑块通过连接块访问附近通信资源,连接块通过可编程交换结构或多路复用器将逻辑块输入/输出信号连接至全局路由结构。连接块(如图1.6所示)允许将逻辑块输入/输出信号分配至任意水平或垂直路径,增加了布线灵活性。

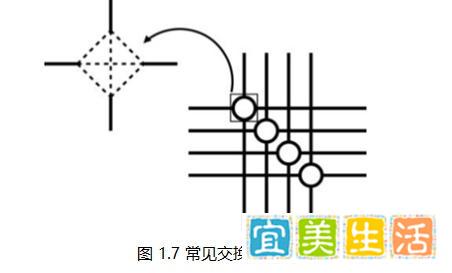

如图1.7所示,交换块位于水平和垂直布线路径交汇处,通常为可编程矩阵开关,允许一条路径信号连接至另一条路径。交换模块设计是一个完整研究领域,产生多种设计,呈现不同连通性和效率,但详细讨论超出本书范围。

分段互连本质上是最近邻结构的改进,仍基于最近邻通信,但通过连接块和交换块实现互连,而非逻辑块本身。对于长距离信号传输,可配置所有经过的交换块,将不同段切换至直连状态,形成逻辑长导线(如图1.5中红色箭头所示)。

此类互连结构未从根本上改善最近邻结构的延迟特性,但将互连结构与逻辑块分离,可在不消耗逻辑块资源的情况下完成长距离路由。

为改善长距离信号延迟特性,引入更长的直连物理导线。例如,将跨越一个逻辑块的导线长度设为L1,部分分段布线架构中包含可跨过4、8个逻辑块(L4/L8)甚至更长的导线。交换块作为信号中间节点,使信号能在不同距离导线间交换,实现通信延迟小于O(N)(N为传输距离跨越的逻辑块数量),通过减少中间交换节点数量降低延迟。

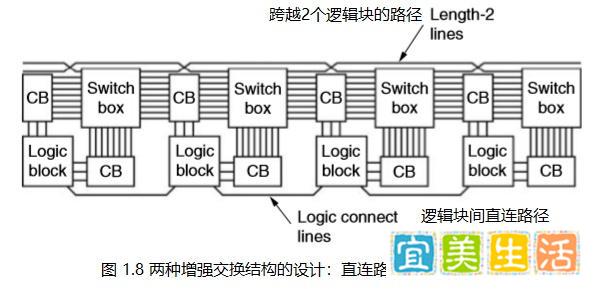

图1.8展示了两种增强互联性的设计:逻辑块间直接连接路径和长度为2(L2)的连接路径。直连路径可节约路由资源,L2路径允许信号在相同交换延迟下传输更远距离。此类架构接近Xilinx XC4000系列商用FPGA。

层次化互联结构 Hierarchical层次化结构采用不同方法减少长距离信号传输延迟。如图1.9所示,在层次结构底层,2×2逻辑块阵列组成一个簇(cluster),簇内仅支持本地路由或最近邻路由。4个簇形成更大的2×2簇集群,包含16个逻辑块。在簇集群边界布置较长导线,连接内部逻辑簇与其他簇集群。此模式在更高层次重复,形成更大簇并设置更长导线连接各部分。

层次化互连模式基于以下假设:设计良好且布局合理的电路主要与相邻块连接,仅需有限数量长距离信号传输。通过在更高层次提供较少跨区域路由资源,此结构在保持区域效率的同时,通过保留长布线路径最小化长距离信号延迟。

在分段体系中,连接不同路由层次的连接点可位于互连结构任意位置,可在现有交换块中创建新跨层次连接点,或布置独立跨层次交换站点以连接不同层次逻辑块。

1.2.2 可编程性 Programmability

与商用FPGA中的逻辑块类似,互连结构中的每个交换点均可编程。在连接块内部,可编程多路复用器选择逻辑块输入并决定输出路由路径;在交换块中,垂直和水平路由路径间的连接通过可编程开关切换;最后,通过可编程交换结构在不同长度和层次结构的路由路径间切换。所有可编程点均采用SRAM数据比特保存用户配置值,后续章节将详细讨论配置比特。

1.2.3 总结 Summary

可编程互连路由资源与FPGA逻辑计算资源对应:逻辑资源用于算术和逻辑计算,互连结构接收逻辑块输出结果并作为输入路由至其他逻辑块。通过布局逻辑块并通过可编程互连结构连接,FPGA可实现复杂数字电路。空间分布计算的本质是将计算任务分布于整个FPGA物理空间。

当前商用FPGA通常混合使用上述互连架构以提供灵活路由资源。实际实现中,分段和层次结构的面积与连接数未必呈对数缩放。现代FPGA中,芯片面积主要由互连结构决定(约90%硅片面积用于互连,仅10%用于逻辑)。在此背景下,互连体系结构的重要性日益凸显,尤其是从延迟角度考虑。

下一篇:fpga是什么专业学的?