时间:2026-04-11 来源:FPGA_UCY 关于我们 0

一、预备知识-补码 &有符号数

涉及到有符号数的运算时,补码是一个非常重要的概念,也是最容易混淆的概念,我们以3位的二进制数为例,首先,无论你是正数还是负数,这些在数字电路里都是无法直接体现的,数字电路里处理的终究是二进制序列,首先3位二进制数可以表示8种状态,无符号数就不说了,肯定是表示0-7八个数,如果是有符号数,注意二进制的序列依旧不变,只是三位中取了第一位做符号位,还是能表示8个数,但是有个特点是,负数能表示的最大值比正数能表示额度最大值绝对值多1,这就是补码表示的特点,例如3位的话就是表示-4到3。

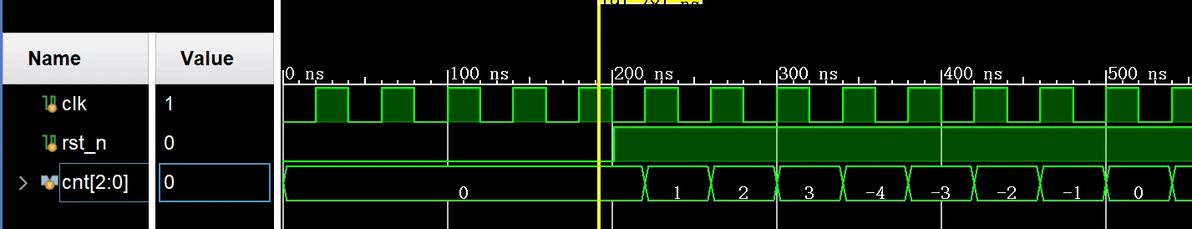

即如果递增从000一直加到011(3),再往下加就不是4了,而是会掉到100(-4),然后-3,-2,-1回环到0。因为有一位被用做了符号位。我们看看仿真,一个简单的计数器:

这里补充一点无论你是负数还是正式,在数字电路里都是补码表示。

正数的补码和原码相同,直接就是二进制原码。

如果想知道某个负数的补码形式,就用模减去这个负数的绝对值,得到的数的原码就是该负数的补码形式,还是以3bit为例,我想知道-3的补码,首先三位二进制的模是2^3 = 8。

8(模)-3(待求负数的绝对值) = 5(101),即101就是-3的补码形式,这是补码最本质的原理,补的名字来源于相加等于模,我们常说的取反加1求补码也是这个原理。

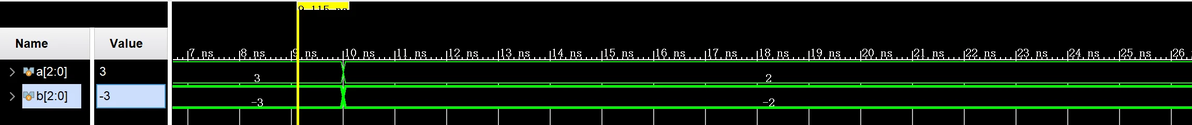

那么我们如果在Verilog中写assign a = -b;其中a是无符号数,3bit,a=3,则这句语句的作用其实就是对a求相反数,本质上是计算了8-a,b会得到101

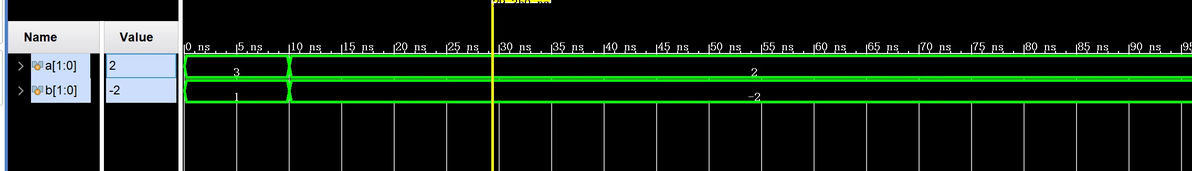

但是要注意,这里取反的对象是正数,而且a已经是3bit了,所以a和b位宽可以一样,但是如果a是2bit(2bit也可以表示2和3),这个时候必须给b多分配一位,因为如果b是两位的话,b只能表示-2到1,-3就不能表示了,这个要根据实际情况来判断,通常如果对正数取反,取反后的位宽总要比被取反的数的位宽给多一位。

可以发现位宽不够的时候,b无法表示-3。

位宽多一位之后就可以表示了。

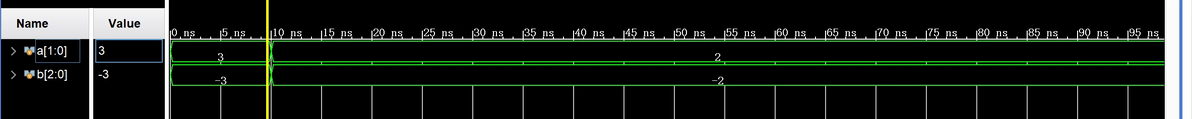

而如果被取反的对象是负数,则取反后的数位宽可以和取反之前的位宽数一致。因为负数表示为正数之后变成无符号数,不需要符号位表示,相当于本来就比取反前的数多了一个位宽表示,肯定可以表示。

取反语句:正取反,结果最好多加1位,负取反,取反前后位宽相同。

取某个负数的补码:模-该数的绝对值 得到的原码即该负数的补码。

二、芯片设计中的定点化

为什么要定点化?因为运算中经常遇到浮点数,而出于计算的高效性,通常将浮点数定点化(数字电路中没有小数点的概念,只会不断进行0和1的计算),除了定点化这种方法也可以使用IEEE754的浮点数格式处理,而定点的位置决定了精度和系统的性能,所以RTL要和理想的算法模型进行比对,误差小于某个范围便可忽略,用于权衡精度和速度。

这里我理解的定点化是给二进制序列作一个定标,即确定小数点的位置,刚刚也说了,因为数字电路中并没有小数点的概念,而我们设计芯片的创造者需要人为规定小数点的位置在哪。举个例子,例如一个无符号二进制序列:4’b0101,在设计的时候我规定小数点在这里4’b01.01(注意,在数字电路中体现不出来,这个小数点在我们自己的脑子里),则表示的就是1.25,而在数字电路中其还是当作整数5来例如4’b01.01+4’b01.10,在数字电路中其还是当作5+6来运算,运算结果为4’b1011,即11,但是按照我们约定的小数点位置,即10.11,结果为2.75,即4’b01.01(1.25)+4’b01.10(1.5),显然,当定点数位宽确定的时候留给小数的位数越多,能表示的精度就越大,但是能表示的范围也会小,故字长、精度、表示范围经常需要衡量。

如何确定字长?例如一个模块中要求最大可以到达100,要求精度是0.001。该选取多大的位宽?答:遇到这种问题时直接使用Log2(N)计算,先用log100向上取整,得到7位,即7位整数位。 -log2(0.001)向下取整得到10。如果时有符号数,再添加一位,共18位。

三、RTL中数据截位的数学意义

例如b,一个四位的RTL中的定点数,假设是13,我们在RTL里直接进行移位b,这样在RTL里右移两位实际上是除4然后向下取整,即floor,即【13/4】=【3.25】=【3】,如果是b=15,会发现【15/4】=【3.75】=【3】,即两种结果是一样的,而实际两者差别很大,这会对算法中RTL中的验证有一定的要求,到底是数值严格相等(因为在rfmodel中通常是高级语言编写的,一般都是Round四舍五入),还是关键性能指标(即有一定的误差范围),这是需要考量的。

上一篇:化工仪器网

下一篇:安徽中科光电色选机械有限公司