时间:2026-04-01 来源:FPGA_UCY 关于我们 0

一、概念介绍:加法器的定义与核心定位1. 基本定义

加法器(Adder)是数字电路中用于实现二进制数加法运算的核心运算单元,是算术逻辑单元(ALU)的基础组成部分,也是计算机、微控制器、数字信号处理器等各类数字系统的核心构件。其核心功能是接收两个或多个二进制输入信号,按照二进制加法规则计算出求和结果及进位信号(若有)。

2. 核心定位与应用场景3. 中英文对照与关键术语

中文术语

英文名称

定义说明

加法器

Adder

实现二进制加法运算的数字电路单元

半加器

Half Adder

仅处理两个 1 位二进制数相加,不考虑低位进位的加法器

全加器

Full Adder

处理两个 1 位二进制数及低位进位,输出和与高位进位的加法器

串行进位加法器

Ripple-Carry Adder

由多个全加器串联组成,进位信号逐位传递的多位加法器

超前进位加法器

Carry-Lookahead Adder

通过逻辑电路提前计算进位,减少延迟的高速多位加法器

进位输入

Carry In(Cin)

来自低位加法运算的进位信号

进位输出

Carry Out(Cout)

向高位传递的进位信号

和输出

Sum(S)

两个二进制数相加后的本位结果

二、原理阐释:从基础到复杂的实现逻辑1. 二进制加法规则(核心前提)

二进制加法遵循 "逢二进一" 原则,基础运算关系如下:

当进行多位二进制加法时,除最低位外,每一位都需要考虑来自低位的进位,这是全加器与半加器的核心区别。

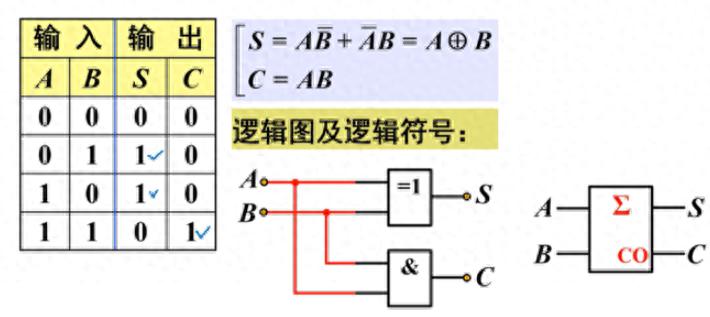

2. 半加器(Half Adder):1 位加法的基础实现(1)核心功能

仅处理两个 1 位二进制数(A、B)的加法,输出本位和(Sum)与进位输出(Cout),不支持低位进位输入。

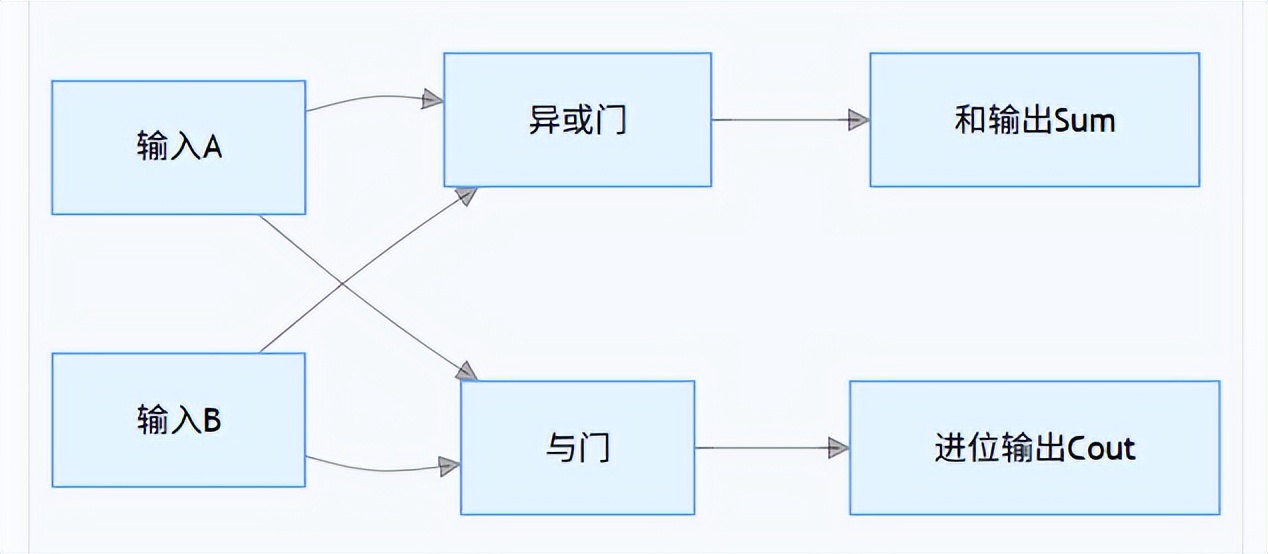

(2)逻辑表达式(3)电路结构

由 1 个异或门(实现求和)和 1 个与门(实现进位)组成,逻辑电路图如下:

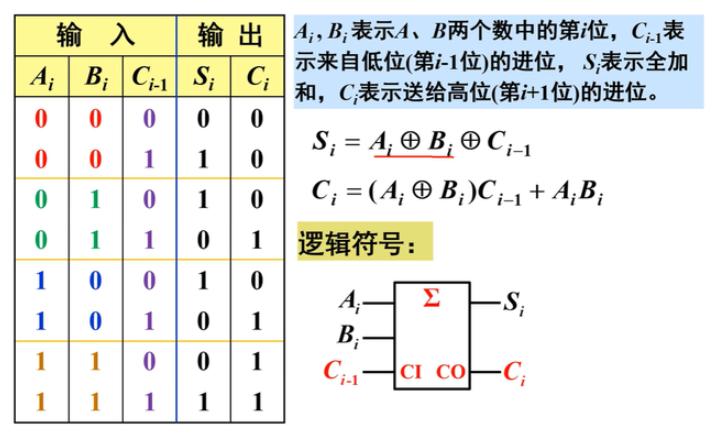

(4)真值表3. 全加器(Full Adder):支持进位传递的进阶实现(1)核心功能

解决半加器无法处理低位进位的问题,接收两个 1 位二进制数(A、B)和低位进位(Cin),输出本位和(Sum)与高位进位(Cout),是构建多位加法器的基本单元。

(2)逻辑表达式(3)电路结构

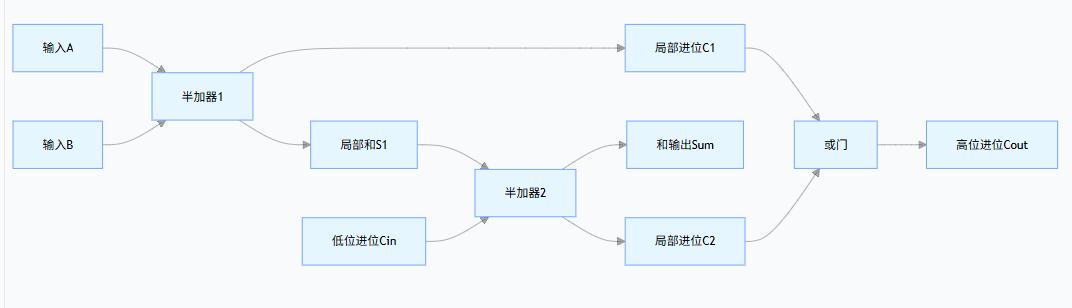

由 2 个半加器和 1 个或门组成:

第一个半加器计算 A 与 B 的局部和(S1)与局部进位(C1);第二个半加器计算 S1 与 Cin 的最终和(Sum);或门合并 C1 与第二个半加器的局部进位(C2),得到最终进位 Cout。

逻辑电路图如下:

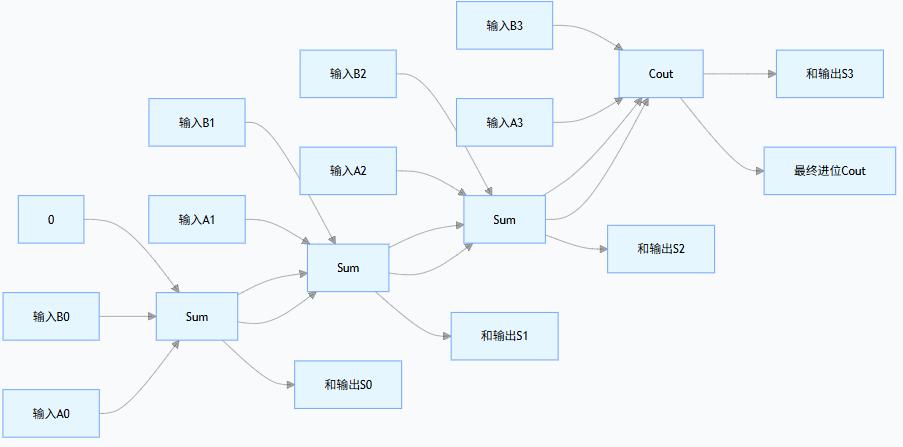

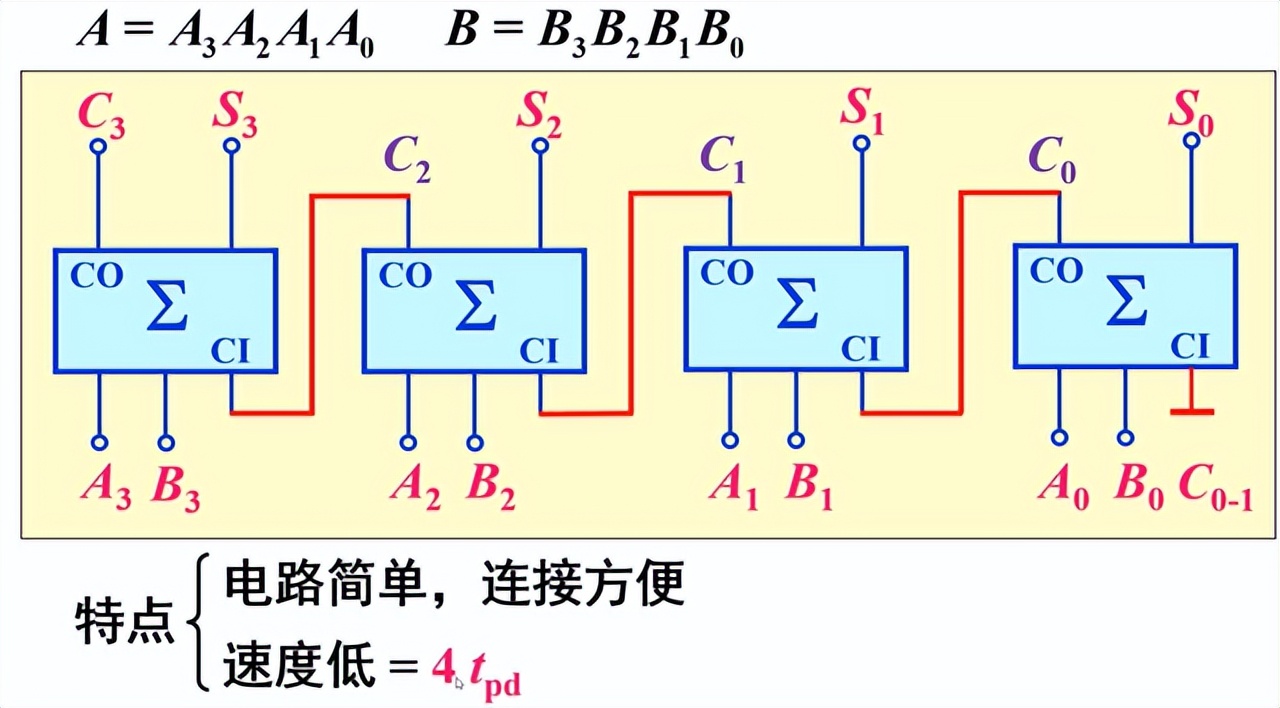

(4)真值表4. 多位加法器:从串行进位到超前进位的进化(1)串行进位加法器(Ripple-Carry Adder)

(2)超前进位加法器(Carry-Lookahead Adder)5. 加法器的物理实现与工具支持(1)硬件实现方式(2)仿真与设计工具三、案例分析:从基础实验到实战应用1. 基础实验案例:Logisim 搭建 1 位全加器(1)实验目标

通过 Logisim 软件,用基础逻辑门搭建 1 位全加器,验证其真值表正确性。

(2)实验步骤打开 Logisim,新建电路,从 "Gates" 库中拖拽 2 个异或门、3 个与门、1 个或门;按全加器电路结构连接元件:异或门 1 输入接 A、B,输出接异或门 2 输入;与门 1 输入接 A、B,与门 2 输入接异或门 1 输出、Cin,与门 3 输入接 A、Cin;或门输入接 3 个与门输出,输出为 Cout;异或门 2 输入接 Cin,输出为 Sum;添加输入引脚(A、B、Cin)和输出引脚(Sum、Cout),设置引脚为 1 位;改变输入 A、B、Cin 的高低电平(0/1),观察 Sum 和 Cout 的输出,验证与真值表一致。(3)实验现象

当 A=1、B=1、Cin=1 时,Sum=1、Cout=1,符合 "1+1+1=11(二进制)" 的运算结果;当 A=0、B=1、Cin=0 时,Sum=1、Cout=0,符合基础加法规则。

2. 进阶实验案例:4 位串行进位加法器的 FPGA 实现(1)实验目标

用 Verilog 语言编写 4 位串行进位加法器代码,在 Vivado 中进行功能仿真,验证其对 4 位二进制数的加法运算能力。

(2)Verilog 代码实现

verilog

// 1位全加器模块

module full_adder(

input wire A,

input wire B,

input wire Cin,

output reg Sum,

output reg Cout

);

always @(*) begin

Sum = A ^ B ^ Cin;

Cout = (A & B) | (A & Cin) | (B & Cin);

end

endmodule

// 4位串行进位加法器模块

module ripple_carry_adder_4bit(

input wire [3:0] A,

input wire [3:0] B,

input wire Cin,

output reg [3:0] Sum,

output reg Cout

);

wire [3:1] carry; // 中间进位信号

// 实例化4个1位全加器

full_adder fa0(.A(A[0]), .B(B[0]), .Cin(Cin), .Sum(Sum[0]), .Cout(carry[1]));

full_adder fa1(.A(A[1]), .B(B[1]), .Cin(carry[1]), .Sum(Sum[1]), .Cout(carry[2]));

full_adder fa2(.A(A[2]), .B(B[2]), .Cin(carry[2]), .Sum(Sum[2]), .Cout(carry[3]));

full_adder fa3(.A(A[3]), .B(B[3]), .Cin(carry[3]), .Sum(Sum[3]), .Cout(Cout));

endmodule

(3)功能仿真与结果3. 实战应用案例:CPU 中的 32 位加法器(1)应用场景

RV32I 单周期 CPU 的 ALU 模块中,32 位超前进位加法器是核心运算单元,负责执行加法指令(add)、立即数加法指令(addi)及地址计算(如 PC+4、基址寻址)。

(2)核心作用加法指令执行:将两个寄存器中的 32 位数据相加,结果写回目标寄存器;PC 更新:计算下一条指令地址(PC+4),保证指令顺序执行;基址寻址:计算内存访问地址(寄存器值 + 立即数偏移量),支持 load/store 指令。(3)性能优化

采用超前进位结构,32 位加法的进位延迟仅取决于逻辑门级数,而非位数,确保 CPU 在单个时钟周期内完成指令执行,满足 50MHz 以上的工作频率要求。

4. 趣味案例:用 ROM 实现简易加法器(1)设计思路

利用 ROM 的地址 - 数据映射特性,将两个输入数拼接作为 ROM 地址,地址对应的存储单元预存加法结果,本质是 "查表法" 实现加法运算。

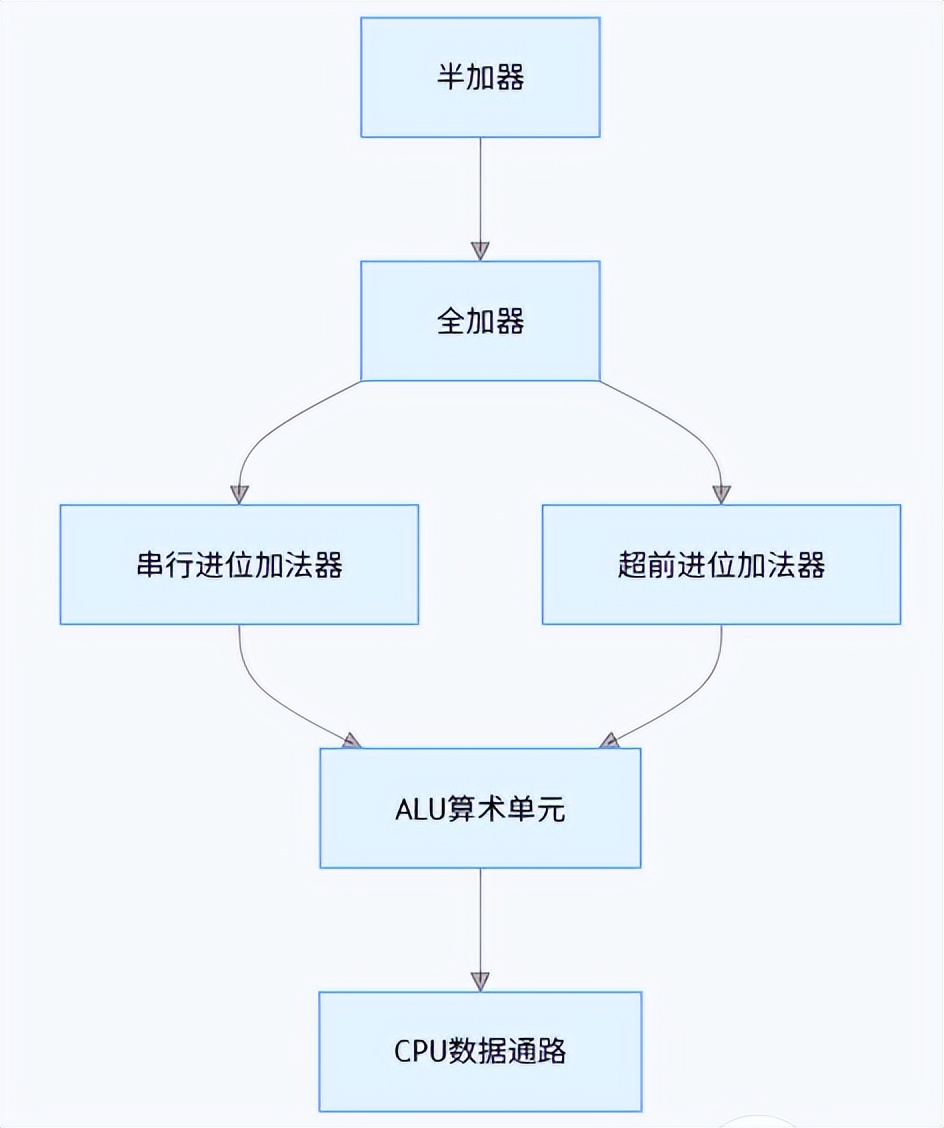

(2)4 位加法器实现(3)优缺点四、知识点总结:核心要点与学习脉络1. 核心知识点梳理(1)加法器层级关系

(2)关键技术对比

加法器类型

优点

缺点

适用场景

半加器

结构最简单,仅需 2 个逻辑门

不支持进位输入,仅适用于 1 位加法

基础教学、简单逻辑电路

全加器

支持进位传递,可扩展为多位加法器

单模块仅能处理 1 位加法

多位加法器的基本单元

串行进位加法器

结构规整,易于扩展,设计简单

进位延迟大,速度慢

低位数、低速系统(如简易计算器)

超前进位加法器

进位延迟小,运算速度快

逻辑复杂,资源消耗多

高位数、高速系统(如 CPU、FPGA)

ROM 查表加法器

设计简单,无需逻辑运算

存储容量大,灵活性差

低位数、低功耗场景

(3)设计关键注意事项时序优化:高位数加法需优先选择超前进位结构,避免串行进位导致的时序违例;资源平衡:FPGA 设计中,需在速度与资源消耗间权衡(如中等位数可采用分组超前进位);接口兼容:加法器输出需与后续模块(寄存器、总线)位宽匹配,进位信号需正确连接;仿真验证:需覆盖所有输入组合(尤其是进位相关场景),确保功能正确性。2. 学习进阶路径基础阶段:理解二进制加法规则,用 Logisim 搭建半加器、全加器,验证真值表;进阶阶段:学习串行进位与超前进位原理,用 Verilog 实现 4 位 / 8 位加法器,进行功能仿真;实战阶段:参与 CPU 或 ALU 设计,实现 32 位超前进位加法器,结合时序约束优化性能;扩展阶段:学习加法器在减法、乘法中的应用(如补码加法、 Booth 乘法器)。3. 常见问题与解决方案

问题现象

可能原因

解决方案

加法结果错误

进位信号连接错误;逻辑表达式写错

检查进位输入 / 输出连接;重新推导逻辑表达式

时序违例(FPGA)

串行进位延迟过大;时钟频率设置过高

改用超前进位结构;降低时钟频率;添加时序约束

资源消耗过多

超前进位加法器位数过多;逻辑门冗余

采用分组超前进位;优化逻辑表达式,减少冗余门

仿真与上板结果不一致

未考虑 FPGA 片上资源特性;未添加约束

参考 FPGA 数据手册;添加 IO 约束、时钟约束

五、总结

加法器作为数字系统的基础运算单元,其原理从简单的半加器到复杂的超前进位加法器,贯穿了数字电路设计的核心思想 —— 模块化、层级化与性能优化。掌握加法器的设计与实现,不仅能理解数字运算的底层逻辑,更能为后续学习 ALU、CPU、FPGA 开发等高级内容奠定坚实基础。

在实际应用中,需根据系统的速度、资源、位数要求选择合适的加法器类型:简易场景可选串行进位加法器,高速场景优先超前进位加法器,低功耗场景可考虑 ROM 查表加法器。通过不断实践与优化,逐步深化对加法器原理的理解,最终实现从 "会用" 到 "会设计、会优化" 的能力跨越。

附:

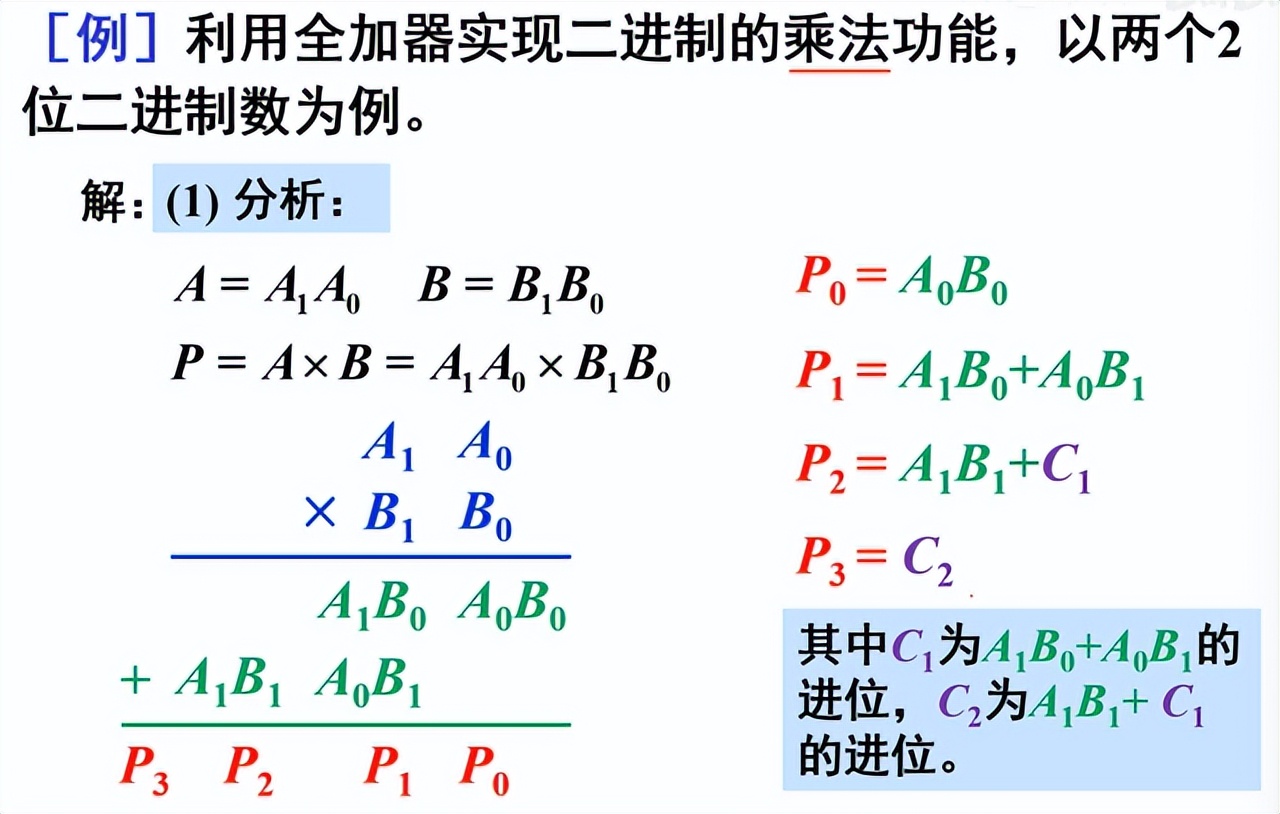

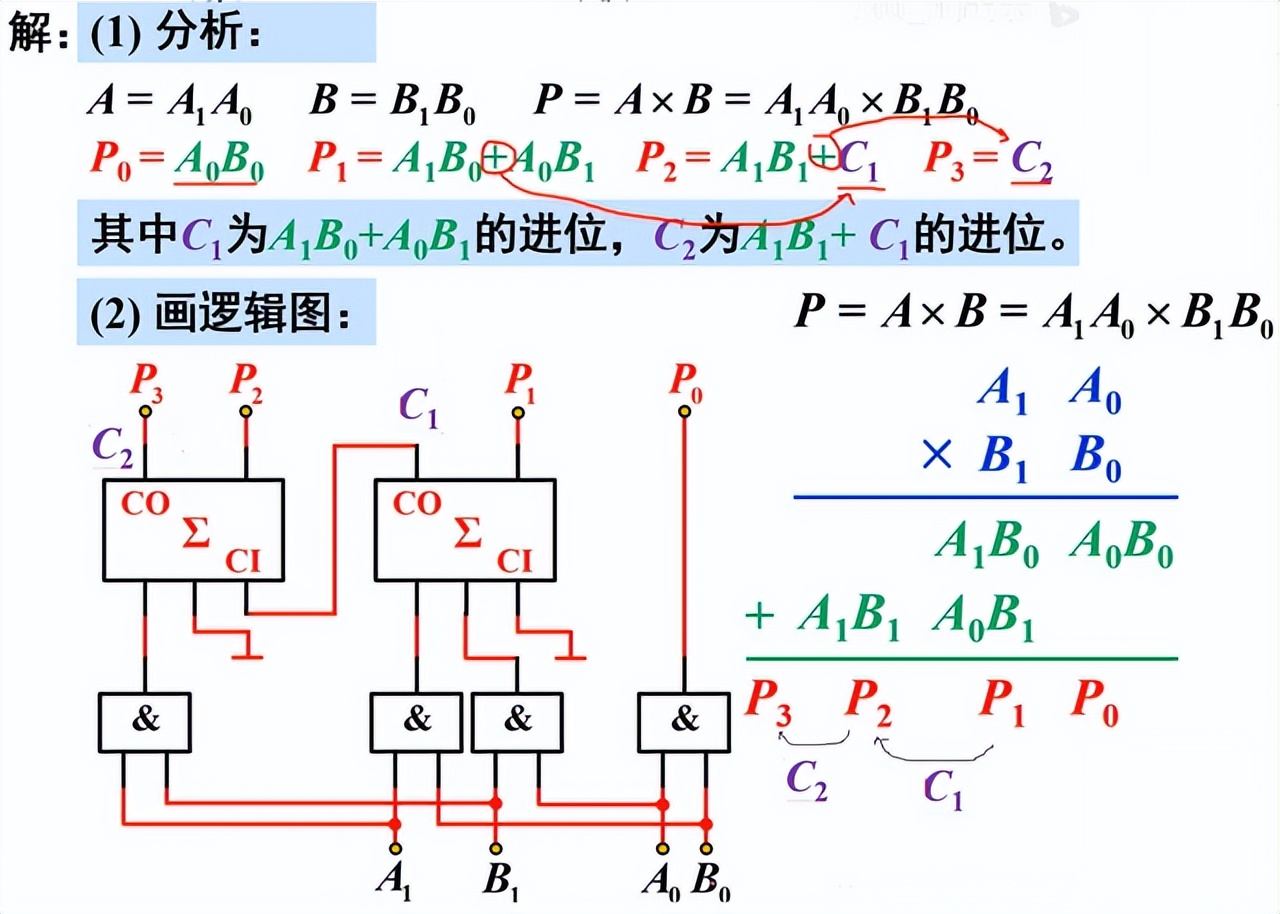

用全加器实现二进制乘法(可类比正常十进制乘法)

串行进位加法器

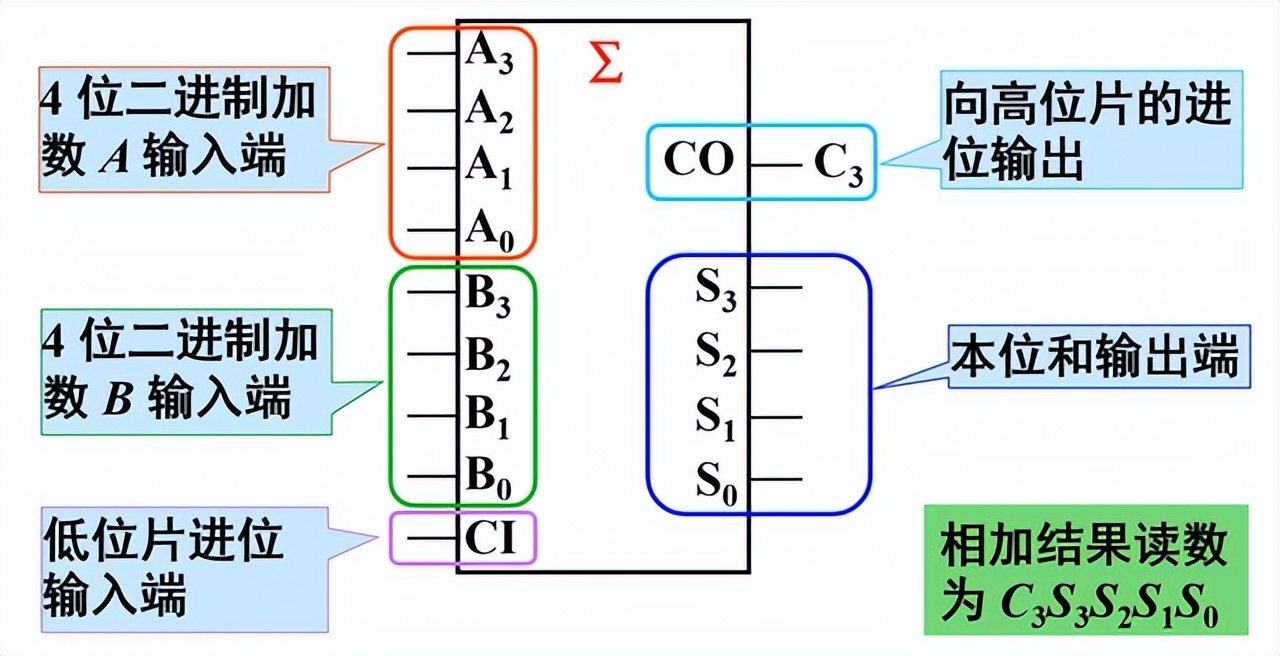

超前进位加法器:74LS283

实践应用案例:用加法器搭建五人表决器加法器 - Bixing's Notebook

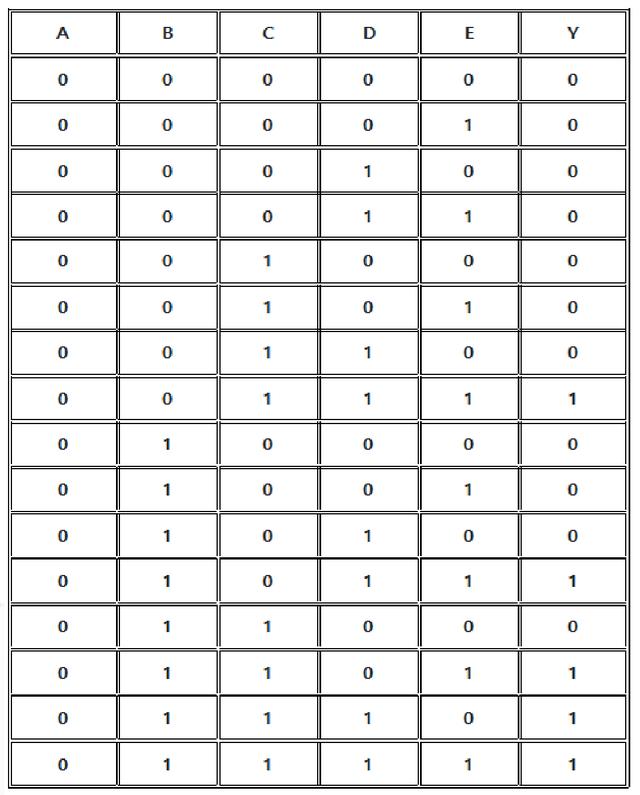

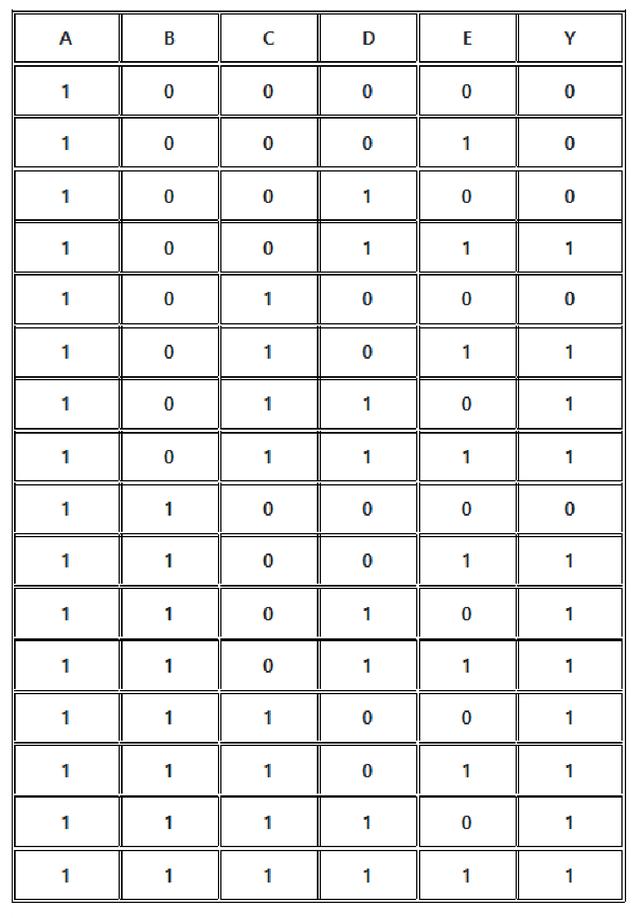

5 人表决真值表(1 = 赞成,0 = 反对;Y=1 表示表决成功)

表格较长,分为A=0和=1两种情况分别列出:

A=0

A=1

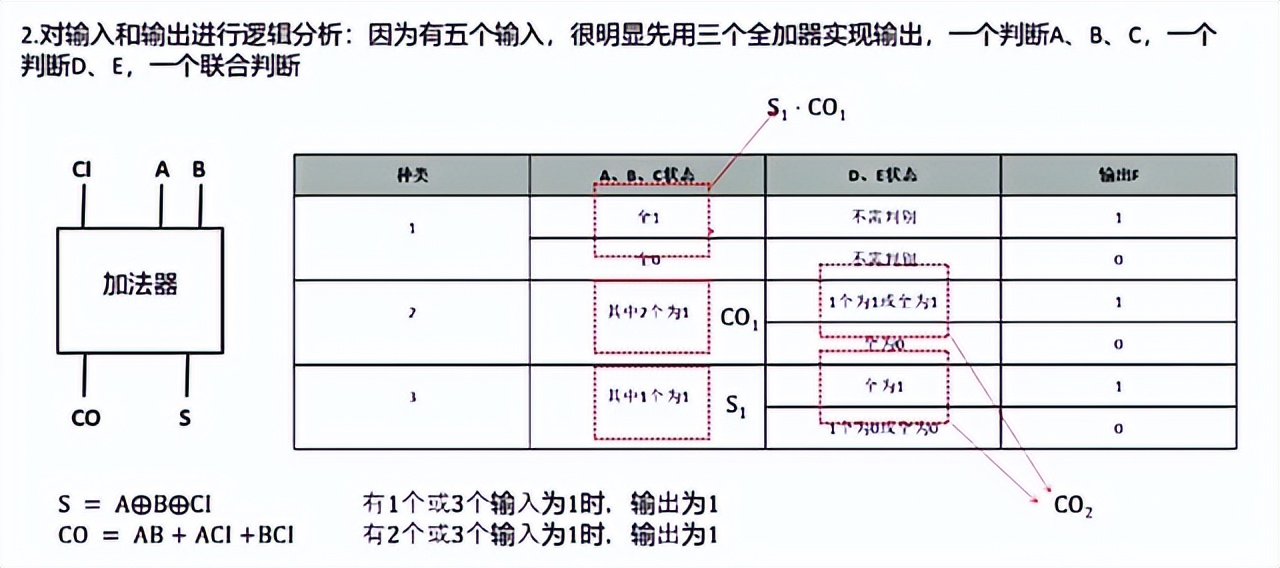

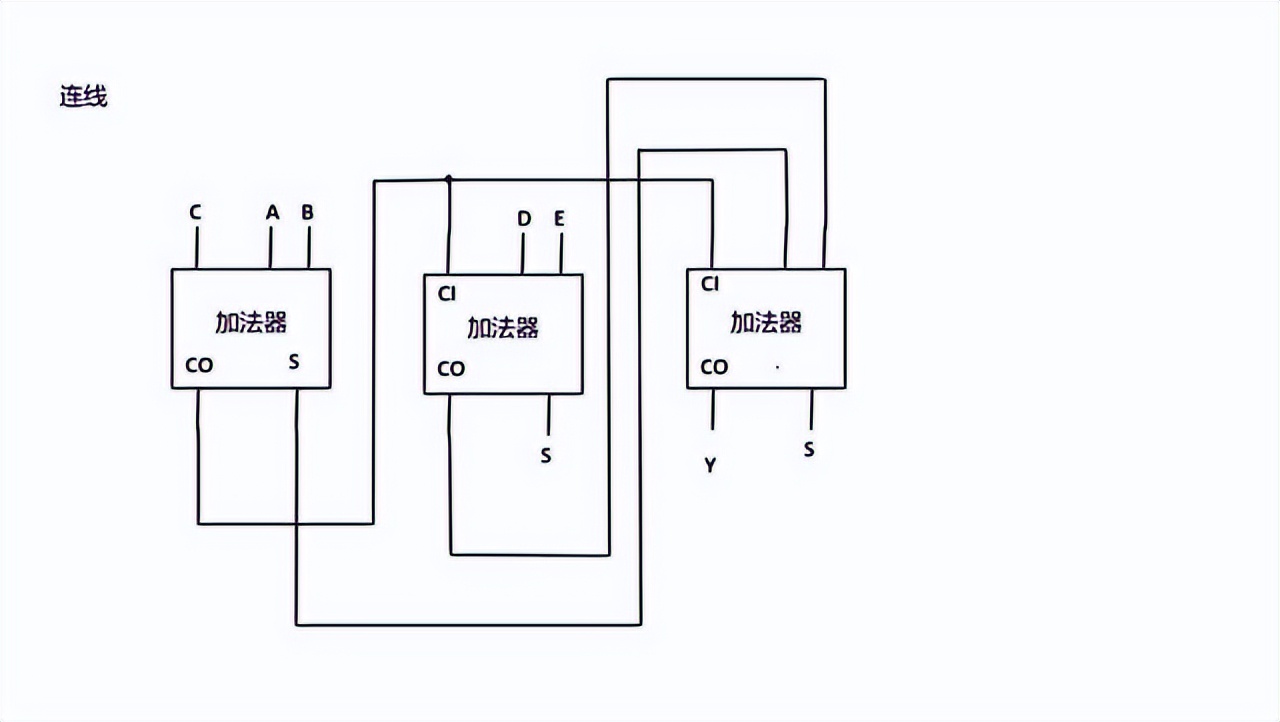

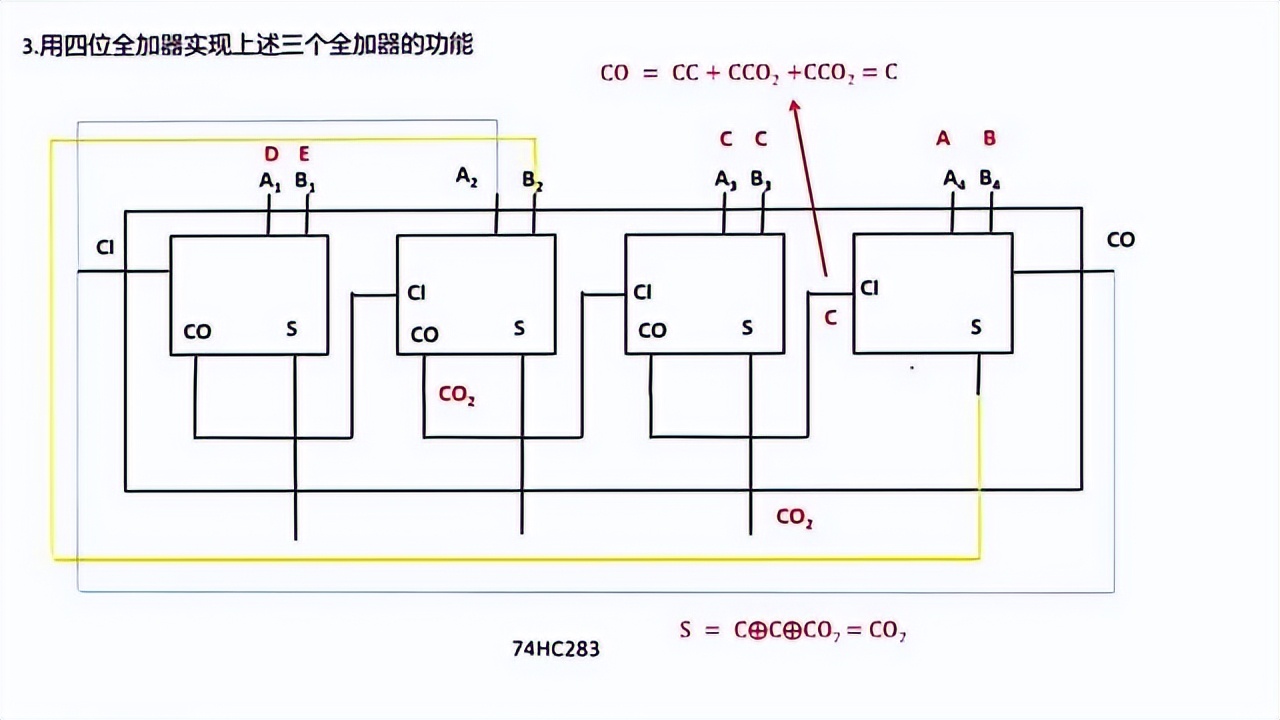

分类简化逻辑运算,先用一个加法器判断A、B、C,一个加法器判断C、D,再用一个加法器对上述两个的结果进行联合判断: