时间:2026-02-16 来源:FPGA_UCY 关于我们 0

前言

只是给自己用,就当是我的学习记录和学习笔记,非教学(我也没本事教)

应该会比较功利式的学

第一篇

1. FPGA简介

2. Verilog HDL基础

1. FPGA简介:略

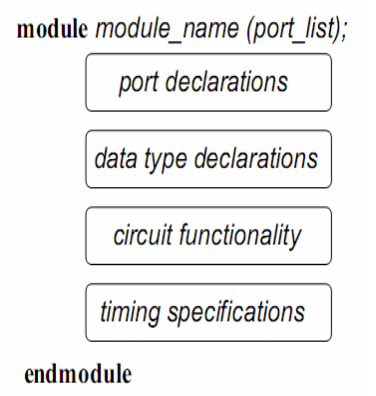

2. Verilog HDL基础

基本要素

Verilog HDL基本要素

2.1 Verilog逻辑值

逻辑 0:表示低电平,也就是对应我们电路的 GND

逻辑 1:表示高电平,也就是对应我们电路的 VCC

逻辑 X:表示未知,有可能是高电平,也有可能是低电平

逻辑 Z:表示高阻态,外部没有激励信号是一个悬空状态

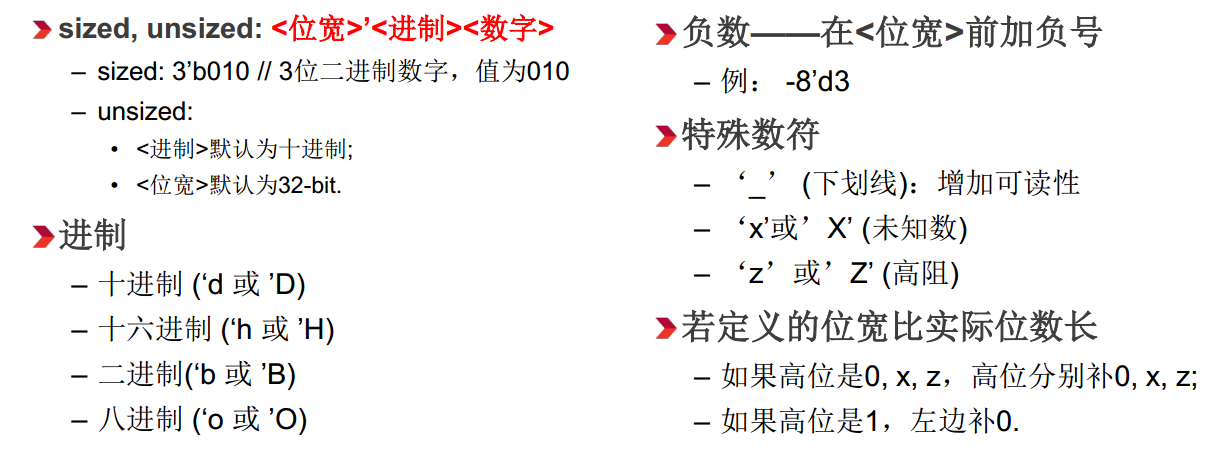

2.2 数字进制

二进制: 4’b0101 表示 4 位二进制数字 0101

十进制: 4’d2 表示 4 位十进制数字 2(二进制 0010)

十六进: 4’ha 表示 4 位十六进制数字 a(二进制 1010)

当代码中没有指定数字的位宽与进制时,默认为 32 位的十进制,比如 100,实际上表示的值为 32’d100

截取一页图片或许更清晰

Verilog数字表示

2.3 Verilog数据类型

(1)寄存器型

(2)线网类型

(3)常量(参数类型)

常被用于定义状态机的状态、数据位宽和延迟大小等

参考

《搭建你的数字积木—数字电路与逻辑设计》

正点,野火,芯路恒等网络上各种教程资料