时间:2026-01-08 来源:FPGA_UCY 关于我们 0

FPGA,即"现场可编程门阵列"(Field Programmable Gate Array)。一种开发者在短时间内利用个人电脑就可以在其上面实现自己想要的功能,而且可以多次重写的廉价设备。

FPGA通过将用户设计的逻辑信息和布线信息加载到内置SRAM型存储单元结构的存储中,使回路按照设计作动。

与需要投入巨大成本和精力的方式不同,一旦用户创建了具有多个FPGA的原型板,就可以立即运行您设计的新架构。而且,修正和更改规格也变得轻松简单。

与ASIC的概念截然相反,FPGA的概念是在短时间能以低成本让用户得到想要的逻辑,这一概念得到了用户的支持。

FPGA的工作原理

那么,从现在开始我们来具体说明FPGA的工作原理。第一个话题是关于构成逻辑电路的基础—程序。FPGA的程序到底在哪儿呢?对于SRAM型,程序被记录在 FPGA 的闪存或 EEPROM 等外部储存器中。

当SRAM型FPGA上电时,程序文件从外部储存中载入。这里被加载的程序文件称为“Bit Stream Data(比特流数据)”。 这些信息被加载到配置存储器中,该存储器由FPGA中的SRAM型存储器单元组成。被加载的比特流数据的各个bit,成为了在FPGA上实现用户所需要的回路的信息源,它把FPGA设备上的资源进行客户化,从而实现要求的回路。这与PC等CPU的启动过程非常相似。它不依赖于硬件,而是通过连接在外部储存器内的配置数据实现,有很高的普遍性和灵活性。

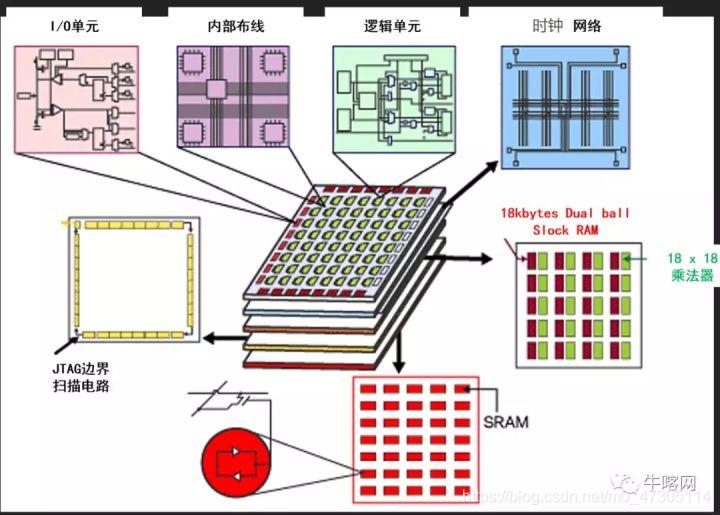

第二个话题是关于FPGA内部结构的说明。FPGA可分为6大部分(如图3),分别为:

I/O:可编程输入/输出单元(I/O单元)

内部布线:丰富的布线资源

逻辑单元:可配置逻辑块(CLB)

时钟网络:数字时钟管理模块(DCM)

JTAG边界扫描电路

块RAM・乘法器:嵌入式块RAM

图3

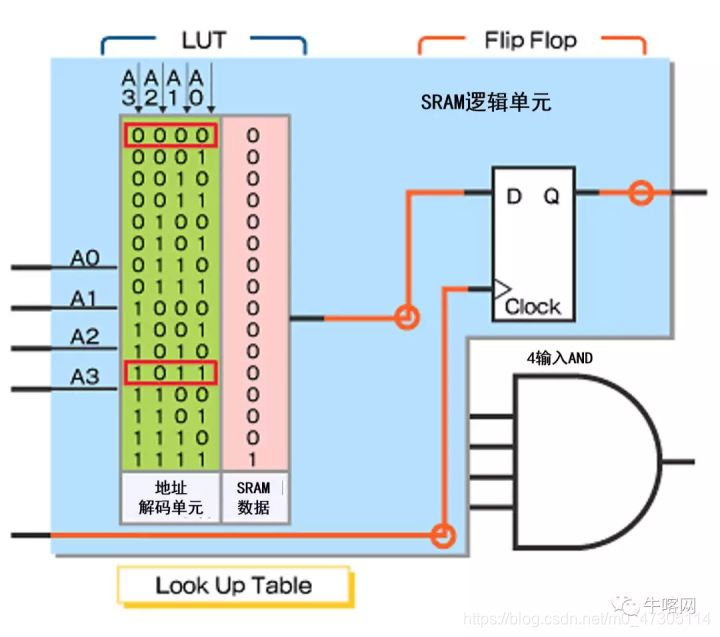

首先,我们针对FPGA的特征“逻辑单元”进行说明(图4)。 FPGA逻辑单元通常由两个4或6输入的“表”(Look Up Table:LUT)和“触发器”(Flip Flop)组成。

图4

一旦SRAM的地址部分有信号输入,就会在LUT中查找对应地址的数据并输出。

图4展示了AND的使用场景。地址全为1的地方,对应写入high(1)的数据,否则全写入low(0)。因此,当输入全部是“1”时,输出始终是“1”。然后触发器再与系统时间同步,输出数据。逻辑单元分布在整个FPGA上,通过内部布线的连接,实现用户期望的功能。

“I/O”主要位于FPGA与外界电路接口的位置,与外部的信号进行信号交换。如今,有超过20种电压等级和规格的I/O可供开发者灵活使用,能自由地实现电路板上的布线。

“内部布线”是通过逻辑单元和I/O单元等的连接,来实现用户的功能。

时钟网络是用于配置FPGA内部时钟的资源。可提供整个FPGA上的全局时钟和本地使用的局部时钟,能在不同的位置实现最佳的电路动作。特别是对于同步电路的设计是必不可少的。

“JTAG边界扫描电路”是为了测试而提供的功能。

“块RAM・乘法器“是用于实现逻辑的资源。如图3所示,FPGA通过在电路内提供均分的块RAM,用户可以不受FPGA内电路的位置限制,进行运算处理和数据保持。

另外,逻辑单元内的查询表不仅可以用作逻辑的实现,还可以当做小型存储器使用(4输入的LUT是16位存储器)。因此,在块RAM之外,可以增加局部存储。在这种情况下,将LUT被称为“分布式存储”。

将以上6种资源组合在一个硅片上,几乎可以在FPGA内不受限制的实现用户所需要的大部分功能。

FPGA的设计流程

这一部分,我们来说明一下FPGA的设计流程。

首先是设计环境。一般设计环境由供应商和第三方提供。主要包括逻辑生成和布线工具两种。

目前,FPGA的逻辑设计绝大多数采用HDL(Hardware Description Language)或Verilog HDL等硬件描述语言设计。 所以在早期,硬件和软件处理在文档设计阶段就是分开的,硬件用HDL,软件用C语言等。

然而,随着处理器和DSP等功能在FPGA内实现成为可能,能够与软件相兼容的硬件设计变得十分必要。在使用统一的语言(比如C语言)进行软硬件的设计之后,合适的任务分解工具(Co Design)变得越发重要,因此软硬件供应商开始协作起来,提供系统级开发环境工具。

FPGA设计流程;首先用HDL之类的语言开始做设计输入,然后使用逻辑综合工具执行设计综合,这个阶段要使用仿真工具进行设计验证

设计综合完成后,将进行设计实施。就是在FPGA内嵌入逻辑电路的具体操作。包括各种功能在逻辑单元上如何实现最有效率(最优)、在FPGA内如何进行配置和布线等,这个阶段决定了FPGA内部的具体配置。

对于高速作动的电路,在这个节点要进行静态时序分析和时序仿真,验证其是否在预期的时间内作动。特别是当作动频率接近极限时,连接逻辑单元之间的布线会导致延迟,因此检查确认是必须的。如果事先知道影响时间的关键点,则可以先在工具上施加约束。

一旦验证了设计在工具上能正常按照要求作动,就可以生成一个编程所需的比特流文件,下载到 FPGA中。也就是使用JTAG之类的下载方式,将比特流文件写入系统的外部储存设备中。

最后是实物测试,由于实际系统是在FPGA和外围电路以及设备交互运行的,因此实物验证和回路验证都是必不可少的。