时间:2025-09-08 来源:FPGA_UCY 关于我们 0

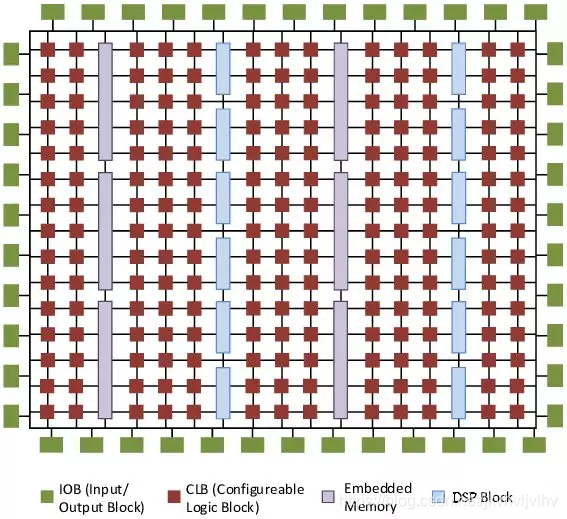

1、首先了解FPGA是什么,Field(现场) Programmable(可编程) Gate(逻辑门) Array(阵列),其中,逻辑门单元是构成一切数字逻辑器件的基本单元,大量的逻辑门单元可以在任何地方随时进行组装的,高度灵活,理论上来讲,只要有足够的资源(积木数量足够多)几乎可以实现数字域的任何功能,受限的是速度、功耗以及系统的成本。

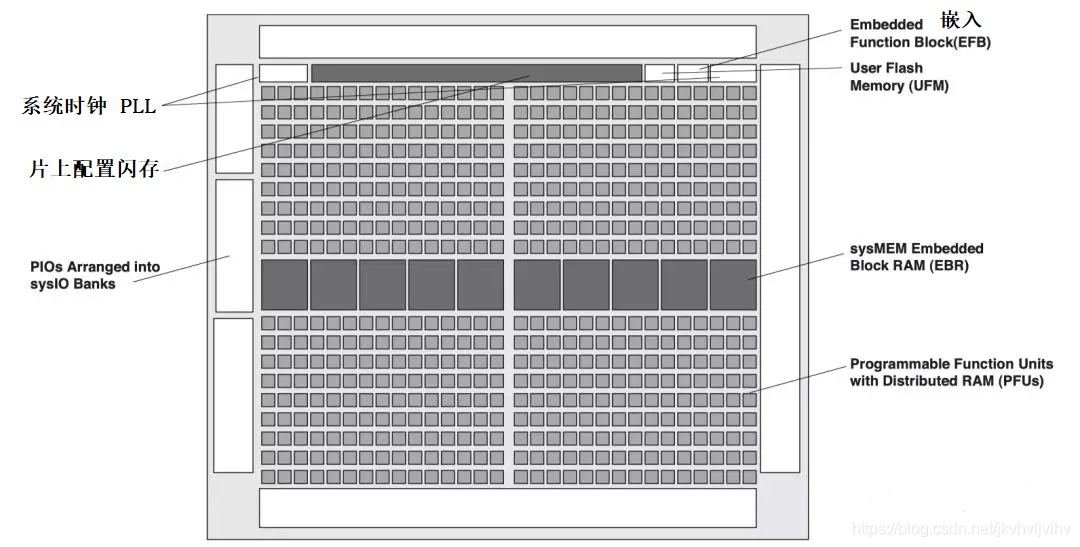

图1 FPGA架构及内部主要功能单元

2、要充分了解FPGA内部功能单元(逻辑单元、存储器、时钟产生、可编程IO等),单元作用、配合方式,针对具体型号,了解该型号的器件内部的各种功能单元具体数量。以Lattice版本为例:

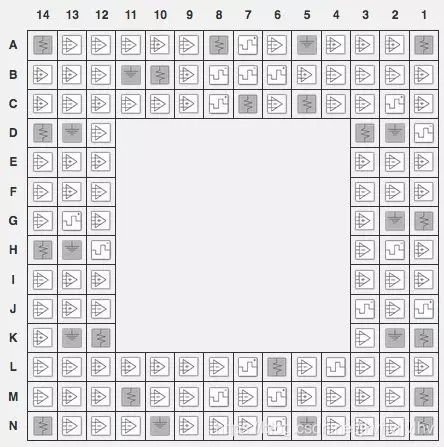

图2 Lattice版本FPGA芯片内部主要功能单元

该器件的具体资源参数如下:

图3 管脚分布

3、数字逻辑的设计思想 - 针对任意一项具体的功能,正确组合器件内的单元,按顺序连接这些单元,需要比较扎实的数字电路/数字系统设计的基础知识以及逻辑思维能力。

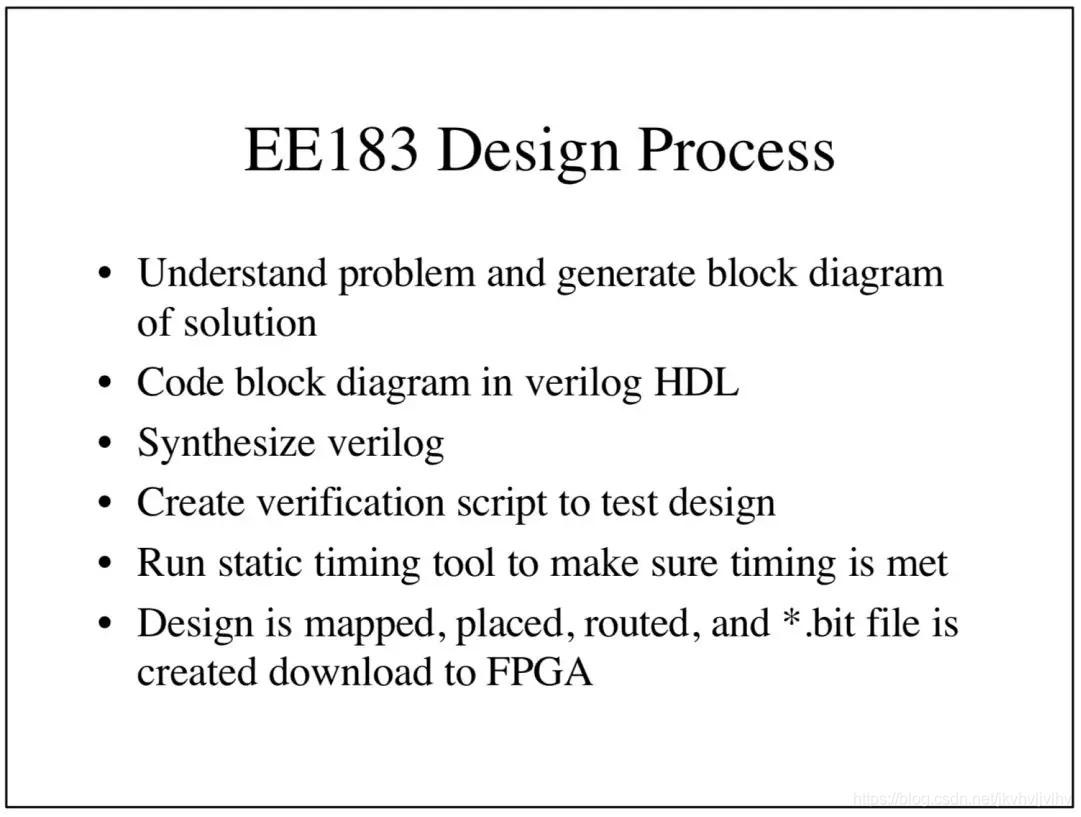

4、需要一些工具来帮助你实现,如一套从头到尾执行的设计环境(FPGA厂商提供的编译工具 - Lattice的Diamond、Intel的Quartus、Xilinx的Vivado),一种连接逻辑思维和机器操作之间的沟通工具 - 设计语言(原理图、Verilog、VHDL等等)。

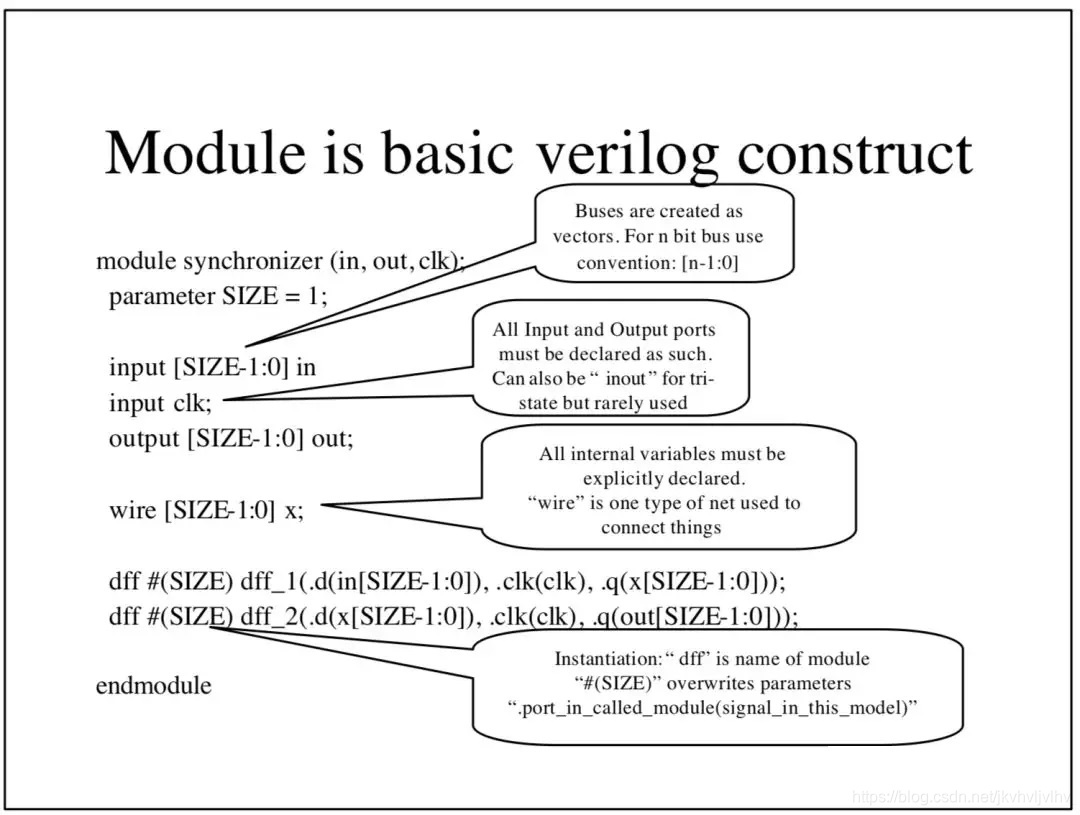

Verilog 是 Verilog HDL 的简称,Verilog HDL 是一种硬件描述语言(HDL:Hardware Description Language),硬件描述语言是电子系统硬件行为描述、结构描述、数据流描述的语言。利用这种语言,数字电路系统的设计可以从顶层到底层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路 ASIC 或现场可编程门阵列 FPGA 自动布局布线工具,把网表转换为要实现的具体电路布线结构。

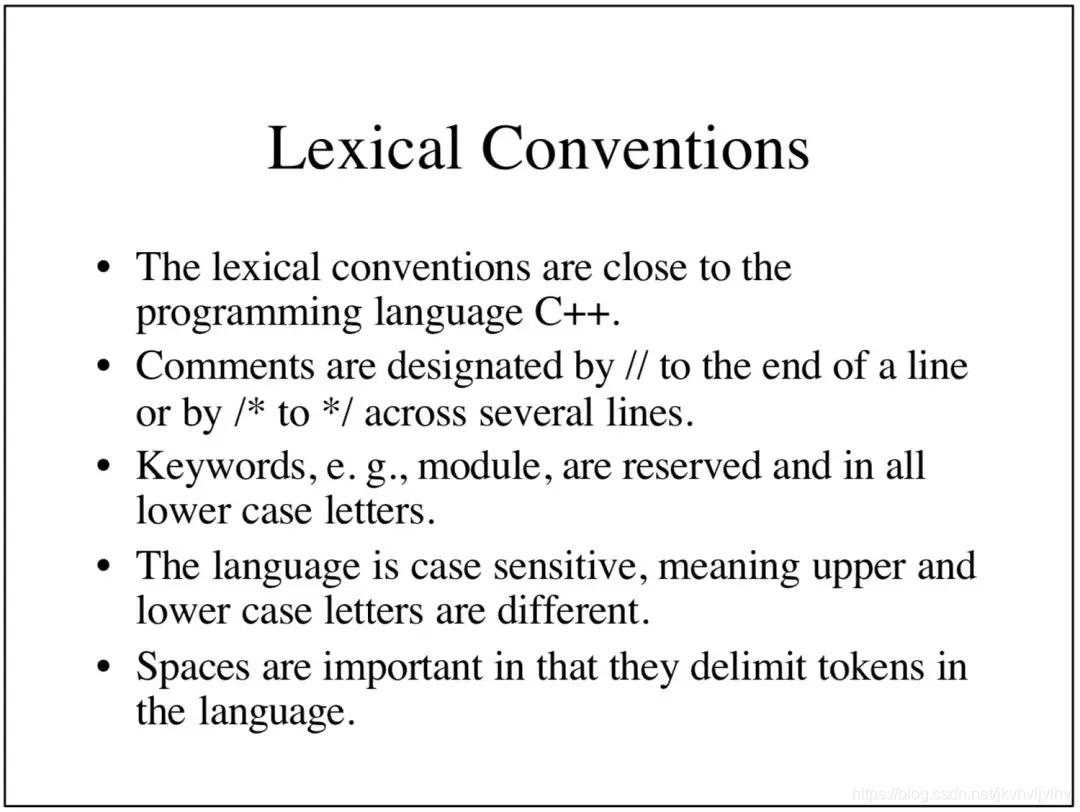

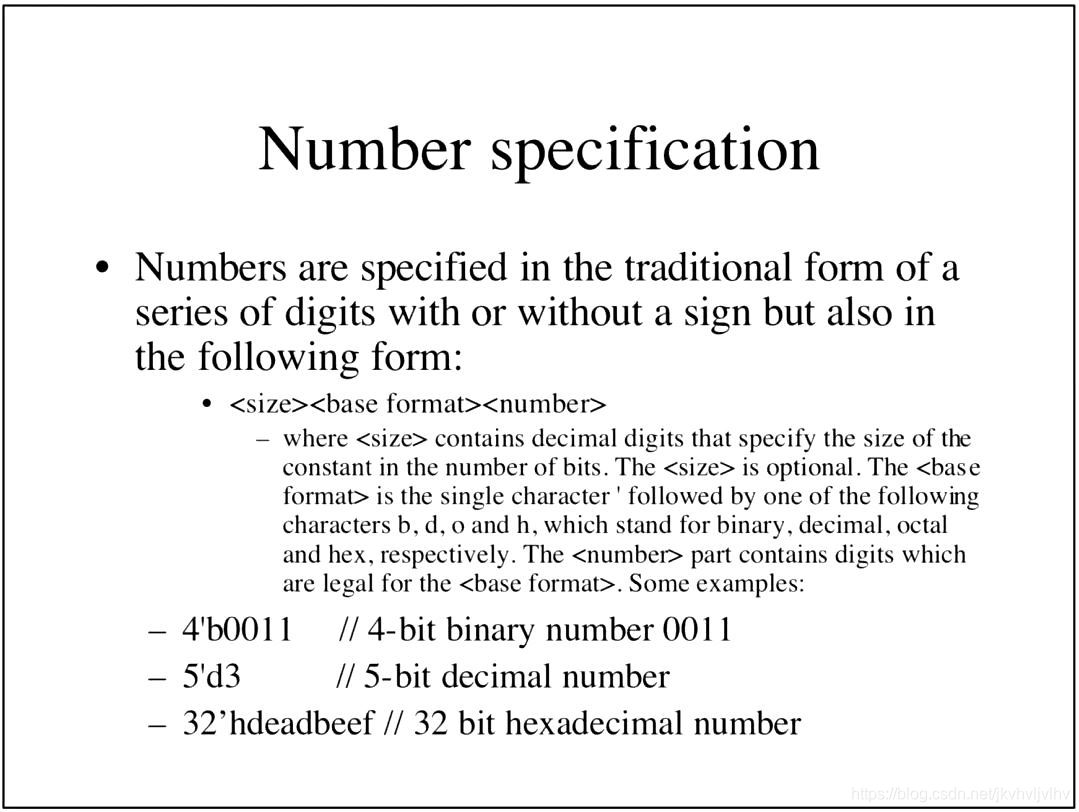

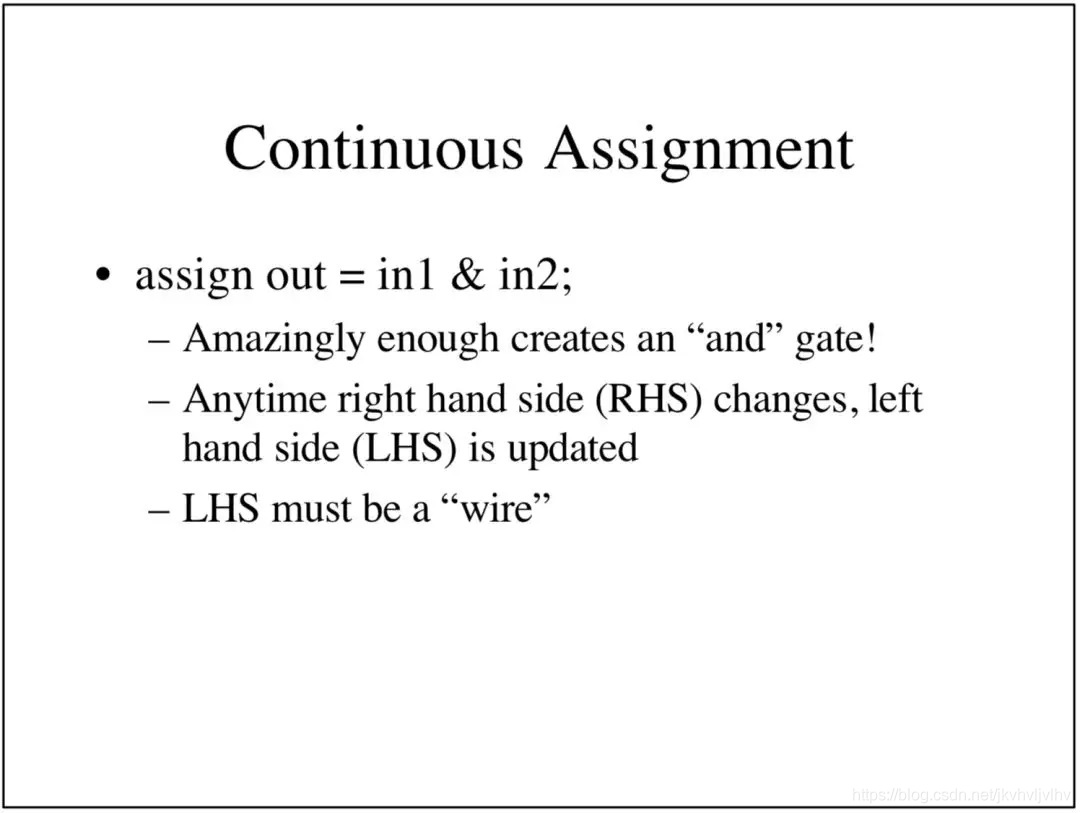

在Verilog编程中需要注意以下几点: