时间:2025-08-11 来源:FPGA_UCY 关于我们 0

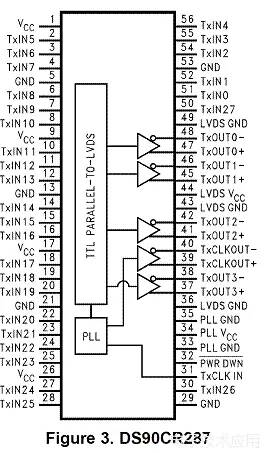

目前电路中数字视频使用Camera Link接口传输,之前的方案是FPGA输出并行数据信号+同步控制信号,再由串化芯片DS90CR287进行并转串处理,处理完通过Camera Link接口输出,采集卡上使用DS90CR288进行并转串处理,这种方式占用FPGA管脚资源多。当传输24bit RGB信号时,需要使用24(信号)+4(同步控制)+1(时钟)=29个管脚,而使用lvds传输,使用altlvds_tx核,只需要5对lvds信号即可,共占用10个管脚。

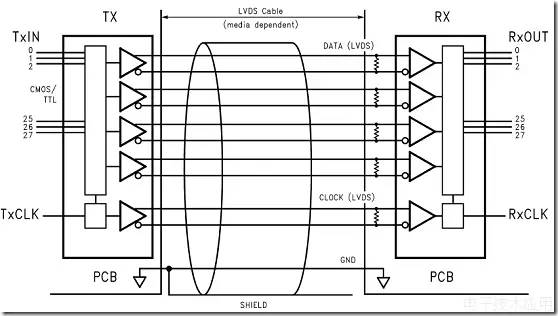

Lvds传输线为双绞线。

现在市场上出现了很多串行AD,并且有多个通道,可使用altlvds_rx核接收数据,想想现在自己设计的板子上还有多个并行AD,真是汗颜啊!!当电路中需要使用多个AD时,如果使用并行AD,板型尺寸大,占用FPGA管脚多,而如果使用多通道(双通道、4通道、8通道)串行AD,板型尺寸可以缩小很多,并且节约FPGA管脚资源,后期的设计中尽量使用这种芯片。

准备设计一款利用FPGA lvds接口传输Camera Link视频信号的电路,前端探测器输出4路模拟信号,使用4路并行AD量化后,FPGA进行处理,再使用altlvds_tx核通过lvds接口输出lvds信号,这些工作作为毕业课题的一部分……后期准备写个lvds在FPGA中的使用连载,记录分享设计过程。

先来介绍介绍lvds的起源,Lvds全称Low-Voltage Differential Signaling 低电压差分信号,1994年由美国国家半导体公司(已被TI收购)提出的一种信号传输模式,是一种电平标准。其主要目的是为了克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点。LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。