时间:2025-07-09 来源:FPGA_UCY 关于我们 0

DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

CPU core:分为2种,软core和硬core。软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。硬core是在特定的FPGA内部做好的CPU core,优点是速度快、性能好,缺点是不够灵活。

RTL级,register transfer level,指的是用寄存器这一级别的描述方式来描述电路的数据流方式;而Behavior级指的是仅仅描述电路的功能而可以采用任何verilog语法的描述方式。鉴于这个区别,RTL级描述的目标就是可综合,而行为级描述的目标就是实现特定的功能而没有可综合的限制。当然,RTL级描述也是采用的verilog,但是是verilog中的可综合子集。既然描述对象是寄存器,就要了解FPGA的基本组成了。

1、搞清楚语法,从宏观要微观都要很清楚,此乃关键,并非有之前说的只占FPGA学习的1/10;

2、从顶层到子模块,弄清楚各个模块的意义;

3、顶层(芯片的输入输出)与子模块,各个子模块的联系:就靠顶层模块的列表,列表外的singnal.

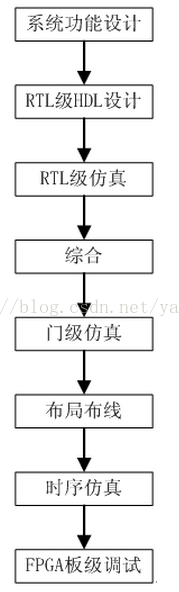

一、开发流程

1) 系统功能设计

在系统设计之前,首先要进行的是方案论证、系统设计和FPGA芯片选择等准备工作。

一般都采用自顶向下的设计方法,把系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元。

2) RTL级HDL设计

RTL级(Register Transfer Level,寄存器传输级)指不关注寄存器和组合逻辑的细节(如使用了多少个逻辑门、逻辑门的连接拓扑结构等),通过描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型的HDL设计方法。

RTL级比门级更抽象,同时也更简单和高效。RTL级的最大特点是可以直接用综合工具将其综合成为门级网表,其中RTL级设计直接决定着系统的功能和效率。

3) RTL级仿真

也称为功能(行为)仿真,或是综合前仿真,是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。

仿真前,要先利用波形编辑器和HDL等建立波形文件和测试向量(即将所关心的输入信号组合成序列),仿真结果将会生成报告文件和输出信号波形,从中观察各个节点信号的变化。虽然仿真是非必需步骤,但却是系统设计中最关键的一步。为了提高功能仿真的效率,需要建立测试平台testbench,其测试激励一般使用行为级HDL语言描述。

4) 综合

所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。

就目前的层次来看,综合优化(Synthesis)是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。

5) 门级仿真

也称为综合后仿真,综合后仿真检查综合结果是否和原设计一致。

在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响。但这一步骤不能估计线延时,因此和布线后的实际情况还有一定的差距,并不十分准确。目前的综合工具较为成熟,对于一般的设计可以省略这一步,但如果在布局布线后发现电路结构和设计意图不符,则需要回溯到综合后仿真来确认问题之所在。

6) 布局布线

实现是将综合生成的逻辑网表配置到具体的FPGA芯片上,将工程的逻辑和时序与器件的可用资源匹配。布局布线是其中最重要的过程,布局将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,并且往往需要在速度最优和面积最优之间作出选择。布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确地连接各个元件。也可以简单地将布局布线理解为对FPGA内部查找表和寄存器资源的合理配置,布局可以被理解挑选可实现设计网表的最优的资源组合,而布线就是将这些查找表和寄存器资源以最优方式连接起来。

目前,FPGA的结构非常复杂,特别是在有时序约束条件时,需要利用时序驱动的引擎进行布局布线。布线结束后,软件工具会自动生成报告,提供有关设计中各部分资源的使用情况。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

7) 时序仿真

是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规(即不满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等)现象。时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。由于不同芯片的内部延时不一样,不同的布局布线方案也给延时带来不同的影响。因此在布局布线后,通过对系统和各个模块进行时序仿真,分析其时序关系,估计系统性能,以及检查和消除竞争冒险是非常有必要的。

8) FPGA板级调试

通过编程器将布局布线后的配置文件下载至FPGA中,对其硬件进行编程。配置文件一般为.pof或.sof文件格式,下载的方式包括AS(主动)、PS(被动)、JTAG(边界扫描)等方式。

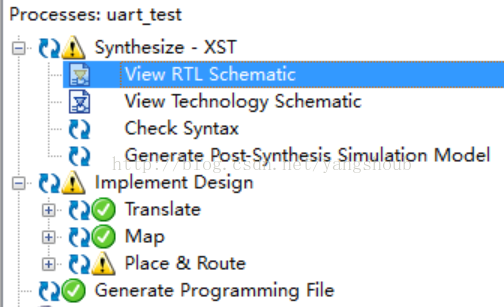

二、与ISE生成烧写文件的过程差不多对应的

Synthesis的下面:

查看RTL原理图(View RTL schematic)

查看技术原理图(View Technology Schematic)

检查语法(Check Syntax)

产生综合后仿真模型(Generate Post-Synthesis Simulation Model)

综合做的工作:

语法检查过程,检查设计文件语法是否有错误;

编译过程,翻译和优化HDL代码,将其转换为综合工具可以识别的元件序列;

映射过程,将这些可识别的元件序列转换为可识别的目标技术的基本元件;

implementation下面:

翻译:将综合输出的逻辑网表翻译为Xilinx特定器件的底层结构和硬件原语。

映射:将设计映射到具体型号的器件(LUT 、FF、Carry等)上。

布局布线:调用Xilinx布局布线器,根据用户约束和物理约束,对设计模块进行实际的布局,并根据设计连接,对布局后的模块进行布线,产生PLD配置文件。

引用:

1、http://blog.csdn.net/loongembedded/article/details/7182900

2、http://www.cnblogs.com/youngforever/p/3155267.html